本文来自微信公众号“半导体芯闻”。

随着半导体行业将重点从2D缩放转向3D缩放,混合键合正在成为实现异构集成的首选方法。

通过在晶圆间直接键合中垂直堆叠小芯片,芯片制造商可以将可实现的互连间距从铜微凸块中的35μm跃升至10μm或更小。这可以将信号延迟降低到可以忽略不计的水平,并实现更小、更薄的封装以及更快的内存/处理器速度,同时消耗更少的功耗。

用于混合键合的工艺工具必须满足关键的工艺规格,例如令人难以置信的平坦300mm晶圆抛光(<1nm中心到边缘的不均匀性)、键合晶圆上的零颗粒、100nm芯片放置精度等。

起步简陋

混合键合十多年前首次在CMOS图像传感器中首次亮相,它将像素阵列芯片与逻辑芯片分离,以最大化背面照明的面积。随后是3D NAND公司,由于现在需要多层的NAND阵列中深窄沟槽蚀刻的限制,这些公司开始使用晶圆到晶圆混合键合。AMD是第一个使用基于小芯片的CPU的混合键合将SRAM堆叠在核心逻辑上的公司。

现在,业界正在努力对8个、16个或更多DRAM的高带宽内存(HBM)堆栈采用混合绑定。这是一场艰苦的战斗,因为需要较低的热预算工艺来防止DRAM刷新性能下降。HBM要求降低沉积温度并在当前300°C至350°C范围以下进行退火。最新进展包括:

●高键能SiCN的低温沉积工艺;

●将形貌控制在1nm以内的CMP工艺;

●(111)取向的纳米晶铜镀层在200°C下结合;

●通过激光和/或等离子切割进行晶圆切割;

●具有高平行度和<200nm精度的芯片到晶圆键合机。

当涉及高带宽内存(HBM)堆栈时,热预算是最重要的问题。美光封装研发主管Wei Zhou表示:“通过用铜对铜连接取代HBM内部的焊料,可以实现更细的间距、更薄的键合线厚度(BLT)以及更坚固的接头。”他解释说,晶圆间键合(每个晶圆上需要相同的芯片尺寸)目前占主导地位,因为晶圆处理更简单,工艺缺陷控制也更好。芯片到晶圆混合键合需要载体晶圆和有机胶层,这通常将热预算限制在250°C或更低。

英特尔最近宣布了新的芯片架构和工艺变更,将混合键合能力从9μm的间距扩展到3μm,这就需要调整电介质叠层,以通过焊盘之间更紧密的间距和间距来提高可靠性;减小键合层厚度以使焊盘金属在退火过程中突出;以及新的CMP配方和浆料,可实现低铜凹陷和光滑的电介质表面。英特尔组件研究中心高级首席工程师Adel Elsherbini及其同事强调了针对清洁度、测试和高贴装精度的三项装配工艺优化。首先,以高测试覆盖率(>99%)对两个晶圆上的芯片进行测试,以最大程度地减少潜在缺陷导致多芯片系统发生故障的可能性。基准标记的大小、形状和对比度被设计到层中。然后,对CMP、切割和表面清洁进行优化,以实现良好的对准和吞吐量。芯片贴装系统的精度取决于主动热控制、控制振动和控制颗粒水平等因素。

工艺如何工作

混合键合的工艺流程开始时与片上镶嵌工艺类似,其中空腔被蚀刻到键合电介质中,然后填充阻挡金属、籽晶和铜ECD。接下来的CMP工艺经过优化,可实现晶圆间的高均匀性,以产生尽可能光滑的介电表面(RMS粗糙度为0.2纳米是理想的),同时在铜中实现几纳米的凹陷(退火时填充),无论条件如何互连图案密度。

接下来,电介质激活步骤使用等离子体生成悬挂的Si-O键,然后进行DI冲洗以水合电介质。接下来,将晶圆2上的KGD与晶圆1对齐并键合,这对晶圆在350°C下退火2小时,然后对顶部硅晶圆进行边缘处理,并使用硅CMP研磨至最终厚度。然后,组装过程可以继续进行RDL,或者可以使用KGD将晶圆键合到另一个晶圆上。

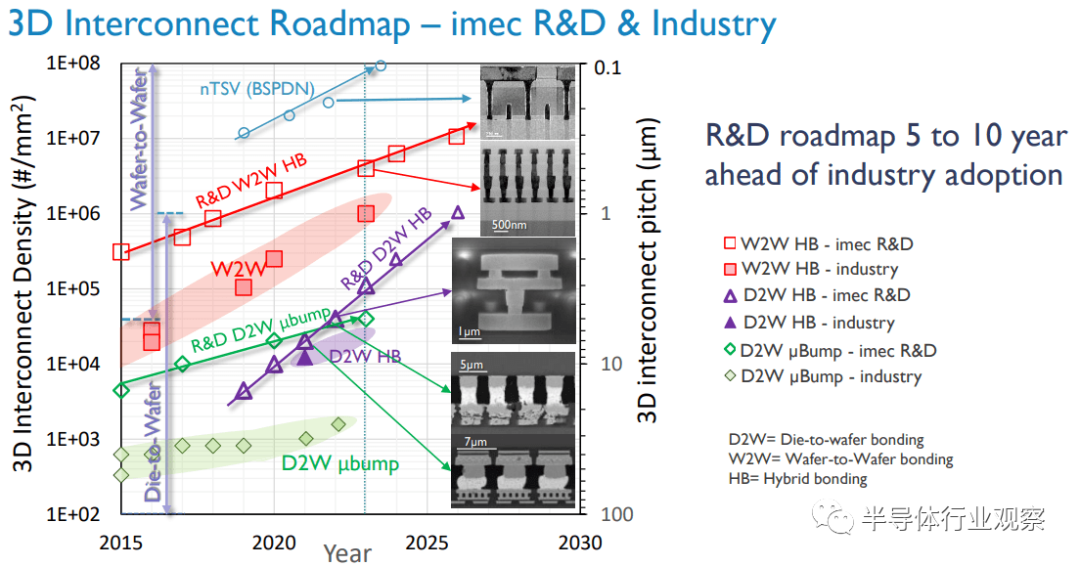

图1:芯片到晶圆混合键合扩展到1μm,晶圆到晶圆混合键合扩展到0.5μm(500nm)间距。来源:imec

混合键合是指在一个键合步骤中同时键合电介质和金属键合焊盘。混合键合有两种类型:一种是晶圆到晶圆键合,这种方式更加成熟,但限制了相同芯片尺寸的组合。第二种是芯片到晶圆键合,它涉及更多的工艺步骤以及将芯片单独放置在载体晶圆或玻璃上(集体芯片到晶圆方法)。

在这两种情况下,通过BEOL金属化处理的两片晶圆都会经历键合电介质的CVD、阻挡层的镶嵌沉积,然后铜填充、电介质的平坦化(带有轻微的铜凹进)、等离子体激活以准备键合、对准、室温键合,并退火以形成铜焊盘的电连接。然后将硅晶圆背面研磨至最终厚度(通常<100nm)、分割,然后进行最终组装和封装。

接合电介质有四种可能的候选材料:二氧化硅、碳氮化硅(SiCN)、氮氧化硅(SiON)。其中,SiCN因其高键合能、良好的防潮性以及优异的铜扩散阻挡性能而成为主要选择。SiCN已被证明能够在较长时间内保持亲水行为,并且可以调整TEOS和Ar/N2 PECVD工艺以获得精确的Si:C:N比例,从而最大限度地提高粘合强度。Applied Materials、Lam Research和SPTS KLA是PECVD系统的制造商。

Imec和SPTS KLA最近开发了一种175°C的PECVD沉积工艺,该工艺在200°C致密化步骤后表现出良好的粘合性能。在可靠性研究中,研究人员确定LT-SiCN的性能优于标准PECVD SiCN薄膜,对于25μm薄膜来说,其TDDB(时间相关介电击穿)行为明显更长。与标准SiCN工艺相比,理想的薄膜含有相对较高的氮含量和较低的碳含量。

铜沉积类似于BEOL金属化的镶嵌铜模块。将势垒金属沉积在电介质侧壁上,然后沉积铜晶种层,然后进行铜电化学沉积(ECD)。Lam Research开发的纳米孪晶铜工艺能够在退火后实现细晶粒连续结构。

芯片到晶圆键合的挑战

到晶圆键合的一个重要层是将底部芯片粘附到硅晶圆或玻璃晶圆载体的临时键合材料。

Brewer Science首席技术官Rama Puligadda表示:“临时粘合材料有一点屈服,因此可以容纳厚度略有不同的小芯片。”她强调,临时粘合和释放层必须具有混合粘合或热压粘合(视情况而定)所有工艺的热预算,然后在粘合后干净地释放,没有残留物或颗粒。“临时粘合材料必须与各种化学物质和高温工艺兼容,例如RDL或成型,而不会发生任何芯片移位。”可以使用机械刀片、激光或更新的脉冲紫外光释放来进行脱粘。

美光科技的Zhou及其同事确定,通过替换用于与无机薄膜临时粘合的有机胶,可以实现更高的热预算、更低的颗粒水平,并且CMP工艺实现了铜凹陷的更大均匀性。平坦化的铜焊盘中需要大约3至5 nm的凹陷,因为铜在退火过程中相对于电介质会膨胀。

铜/电介质CMP步骤是流程中最关键的步骤之一。它决定了待粘合表面的平整度(允许<1nm/μm的滚降)。电介质应具有完全光滑的表面(<2ÅRMS粗糙度)。最重要的是,所有铜焊盘上的铜必须具有统一的凹槽水平。

等离子体表面活化步骤可产生多个悬挂的Si-O位置,从而实现高键合强度(>2.0 J/m 2),而不会氧化铜焊盘或将铜溅射到薄膜的其他部分或工艺室的壁上。三星电子最近表明,氮等离子体活化步骤的压力几乎是氧参考等离子体工艺的2倍,为每边铜垫范围为0.4至0.7μm(方形垫)的SiCN薄膜创造了良好的工艺条件。[3]三星工程师使用反应分子动力学模拟来确定电容耦合射频反应器中的Ar/N 2等离子气流和偏置功率,以提供最容易发生键合的SiCN表面,同时最大限度地减少铜的再溅射。

激活后,用去离子水冲洗晶圆,然后对齐顶部和底部晶圆并在室温下粘合。使用Maszara刀片测试技术测量粘合强度。利用扫描声学断层扫描来扫描粘合界面中的空隙,这些空隙在SAT图像上显示为白点。

键合后,修整键合晶圆边缘并使用硅CMP研磨顶部硅晶圆。在此CMP工艺中,必须严格控制晶圆边缘缺陷。

“晶圆键合后,典型的工艺是在研磨顶部硅基板之前对键合晶圆顶部进行边缘修整。通常很难精确控制边缘修整深度以停止在粘合界面处。在顶部硅片部分研磨后,通常使用反应离子蚀刻(RIE)去除剩余的硅,”应用材料公司的工程经理Kai Ma解释道。

“如果在RIE过程中边缘修整进入底部晶圆,蚀刻剂会在底部晶圆上形成底切。这是因为在边缘修整工艺期间,晶圆边缘的蚀刻停止介电层被去除。如果在到达键合界面之前停止边缘修整,并采用Si RIE工艺去除研磨后残留的硅,则可能会在晶圆边缘斜角区域形成悬挂膜,最终成为片状缺陷。”

工程师发现,通过将边缘修整深度限制在键合界面上方几微米,他们可以去除剩余的硅和斜面薄膜,从而最大限度地减少边缘缺陷。

最后使用刀片切割、激光(隐形)切割或等离子切割方法对粘合芯片进行分割。由于顶部芯片晶圆在放置和键合之前被切割,因此分割方法必须无污染。“减少切割引起的颗粒显然对于这项技术的成功具有重要意义。芯片到晶圆的堆叠过程以顺序模式运行,这意味着仅完成一个存储晶圆堆叠就需要数小时。”Zhou说。此外,即使是小颗粒也可能长大,在粘合界面处形成20倍大的空隙,从而阻碍粘合。美光集团决定首先使用激光切割在街道上刻划多个介电薄膜,然后对硅块进行等离子切割。

工程师用于解决加工过程中颗粒生成问题的另一种方法是沉积保护层,例如光致抗蚀剂或其他材料,该保护层在下一个加工步骤之前被去除。

结论

混合键合工艺(包括电介质PECVD、铜ECD、CMP、等离子体激活、对准和键合以及分割)都涉及严格的薄膜质量规范、高水平的清洁度以及确保已知良好的芯片具有高测试覆盖率。尽管该行业在集成这些工艺方面取得了长足进步,但仍将继续寻求较低温度的替代方案,以便HBM等敏感存储器最终能够利用混合键合技术。