本文来自微信公众号“半导体行业观察”。

随着各种新兴应用发展,在终端产品需求多元化与客制化的趋势下,异质整合封装技术在半导体产业扮演至关重要的角色。透过异质整合封装技术,可在更小的空间内整合多种芯片,以达到更佳的效能与更好的整合度。

在高效能运算、资料中心、医疗和航太等应用领域,对于高可靠度、高效能和降低功耗的需求不断提升,因此异质整合封装技术的应用也愈广泛。此外,ChatGPT掀起生成式人工智能(AIGC)热潮,随着AIGC应用普及,人们对高效能运算需求增加。未来AIGC应用所需的运算需求将持续提升,小芯片异质整合架构设计和先进的封装技术,提供更高效的芯片整合方式与封装技术,有效提升芯片的运算效能与可靠性。

异质整合封装的核心技术为先进封装技术,由于半导体产业链上IC设计、电子设计自动化(EDA)、半导体制程、材料、设备等亦为异质整合封装须共同整合的技术,大厂透过筹组产业联盟,积极推动芯片间传输规范的标准化,除可降低设计成本,也让不同厂商、代工厂的晶粒能在单一封装内整合。UCIe联盟与台积电3DFabric联盟就是异质整合封装发展趋势中的联盟。

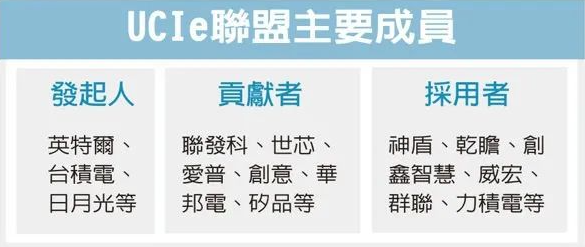

英特尔2022年3月邀请台积电(2330)、三星、超微、微软、Google、日月光等大厂组成UCIe联盟,致力将小芯片资料传输架构标准化,以降低小芯片先进封装设计成本,为未来高阶运算晶片开发主推的小晶片整合技术平台。UCIe联盟目标是制定统一小芯片/晶粒间的传输规范,实现晶粒「随插即用」,满足高阶运算晶片持续提升运算单元密度,以及整合多元功能的需求。

UCIe联盟成立一年就有超过100个会员,包括半导体产业链不同类型的业者。目前成员以美国业者最多,其次依序为中国大陆与台湾;次产业方面以IC设计业者最多,记忆体与IC封测业者次之。

UCIe联盟成员分三个级别:发起人、贡献者、采用者。台湾加入联盟的贡献者包括联发科、世芯、爱普、创意、华邦电、矽品等六家业者;采用者包括神盾、干瞻、创鑫智慧、威宏、群联、力积电等六家业者。作为联盟发起人,英特尔、台积电、日月光等的先进封装技术架构如EMIB、CoWoS、FOCoS,亦将成为未来高阶运算芯片开发主推的小芯片整合技术平台。

图/经济日报提供

另外,台积电2022年10月成立3DFabric联盟,以加速创新及完备3D IC的生态系统。联盟提供开放平台,成员可以共享技术、知识和资源,加速3D芯片堆叠技术发展。该联盟亦提供成员最佳的全方位解决方案与服务,支援IC设计、制造、封装测试、记忆体模组、载板等多个领域的开发。

加入3DFabric联盟的业者包括世芯、创意、日月光、矽品等,以及微软、三星、SK Hynix等国际合作伙伴,共建多元生态系统。

IC设计服务方面,世芯与创意分别提供能支援高效能运算和记忆体需求的先进封装相关服务,以满足AI和HPC市场。世芯2023年1月完成3奈米N3E制程AI/HPC测试芯片设计定案,并提供台积电CoWoS先进封装设计与投产服务。创意2023年4月宣布采用台积电CoWoS-R先进封装技术完成3奈米8.6Gbps HBM3与5Tbps/mm GLink-2.5D IP设计定案。

记忆体方面,华邦电与IC设计服务业者智原合作开发CUBE 3D Memory IP,并于2023年2月宣布提供3DCaaS(3D CUBE as a Service)一站式服务平台,加速客制化边缘运算的发展。力积电则是推出3D架构AIM芯片制程平台,提供逻辑与记忆体解决方案,协助客户缩短AI产品开发时程。

台积电与联电皆致力于异质整合布局。台积电2022年6月启用日本筑波3D IC研发中心,专注研究下世代3D IC与先进封装技术的材料。台积电也积极扩充3D Fabric先进封装产能,预计至2025年无尘室面积规模将扩称至2021年的二倍以上。联电2023年2月宣布与Cadence共同开发3D IC混合键合参考流程,已通过联电芯片堆叠技术认证。

IC封测方面,日月光去年推出先进封装VIPack平台,为异质整合架构提供垂直互连整合封装解决方案。IC载板大厂欣兴则导入多芯片异质整合封装的技术平台。

异质整合封装将不同功能、尺寸的芯片整合至同一个芯片封装中,并透过封装技术实现互联性,提升系统效能、功耗表现与成本效益,是未来高效运算及物联网多元终端应用的重要支持技术。加速异质整合封装的发展,需要国内半导体产业链跨领域多元整合的生态体系,强化不同领域之合作与交流,实现技术整合与创新,从而提升台湾半导体产业的竞争力。