本文来自电子发烧友网,作者/周凯扬。

过去20多年的时间里,图像传感器的开发上已经迎来了不少创新,尤其是在移动市场的冲击下。如今一亿像素、自动对焦、HDR都已经不是新闻了,也正是因为有了智能手机这一商业平台作为支撑,图像传感器开始像手机SoC一样,不仅开始在芯片内加入各种AI/ML技术,也在沿用后者的结构和制造方案,比如芯片堆叠和互联技术。

堆叠式图像传感器的发展

2012年,索尼推出了首款商用BSI堆叠式传感器Exmor RS,让传统图像传感器的各项参数都获得了升级,比如更小的像素尺寸、更高的像素密度,并通过更强大的信号处理与图像重构技术,得到更好的图像性能。

三层堆叠式图像传感器/索尼

图像失真是卷帘快门传感器中经常遇到的问题,这往往是由于像素读取的时间滞后引起的。正因如此,三层堆叠的图像传感器开始出现,将像素层、逻辑层和DRAM叠加在一起。索尼在2015年发布了首款三层堆叠式的CMOS传感器,其像素层、DRAM层和逻辑层分别用了90nm、30nm和40nm的工艺。

三星也在2017年跟进了这一设计,并随后推出了ISOCELL 2L3这一图像传感器,堆叠了一个LPDDR4 DRAM芯片,实现了在1/120秒内以960FPS的速度捕捉慢动作画面。

通过芯片堆叠的方法,图像传感器在一些高端应用上实现了不小的进步,原因之一就是更小的传感器尺寸。再以索尼Exmor RS为例,一个1/4英寸800万像素的CMOS图像传感器。在索尼发表的论文中,其研究人员指出指出堆叠方案让芯片的大小减少了30%。

此外,复杂的逻辑层信号处理电路用到先进工艺,而像素层的像素阵列用的仍是各家打磨多年的成熟工艺,除了维持原有的像素优势外,在信号处理电路中可以增加更多像自动对焦、AI这类的先进功能,实现真正的智能传感器。

像素层再堆叠

2021年底,索尼在IEEE国际电子设备会议上再次发布猛料,宣布成功开发出了全球首个双层晶体管像素堆叠的CMOS图像传感器。传统的堆叠式CMOS图像传感器光电二极管和像素晶体管在同一背照像素层,而索尼这一新技术将两者分离为两层垂直堆叠。

双层晶体管像素堆叠式CMOS图像传感器技术/索尼

根据索尼的说法,这一结构让饱和信号量提升至原来的2倍左右,意味着单像素可以存储更多的电子,因此传感器的动态范围显著提升,并降低了噪点,哪怕是在更小的像素尺寸下,也能保持或提升像素原有的特性,从而提高成像性能。

芯片互联技术的支撑

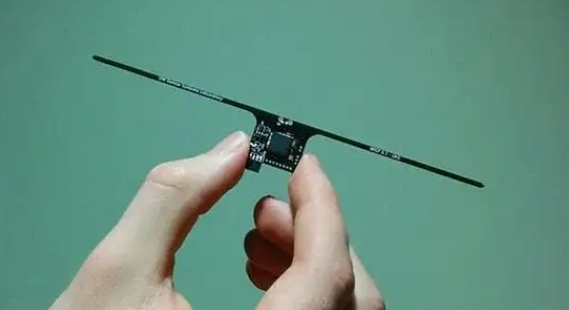

仅仅只是将两个芯片堆叠在一起是不够的,还得靠芯片互联技术在芯片之间创造合适的电路互联。而在图像传感器中,最常见的垂直互联技术就是TSV和混合键合。

TSV,即硅穿孔技术采用的不是走线键合的方式,而是在芯片上钻孔,通过每一层芯片,再加入导电介质形成通道,为芯片之间传递电信号的互联技术。对于不需要提高TSV密度,传输大量数据,也不需要重新设计的图像传感器来说,后钻孔的方法最为普遍。因为后钻孔可以在完成的晶圆上进行,所以可以交由封装厂。

铜混合键合/索尼

混合键合技术近来也开始慢慢普及,无论是豪威还是索尼都开始在新一代产品中使用这一技术,尤其是铜混合键合。以索尼的SenSWIR系列非可见光图像传感器为例,这类SWIR传感器的像素尺寸大于一般的CMOS图像传感器,因此普遍分辨率不高,而铜混合键合缩小了像素间距,降低至只有5μm的像素大小,提供了SXGA(1280x1024)级别的像素分辨率。随着图像传感器继续向像素尺寸小型化、像素精细化的趋势发展,这类混合键合技术也会越来越普及。

结语

芯片堆叠和互联技术已经在图像传感器上得到了广泛应用,支持到更小的像素尺寸、更大的像素阵列和支持ML/AI的智能图像传感器。但与此同时,图像传感器上用到的半导体工艺远没有达到极致,未来的堆叠芯片会拥有更高性能的逻辑电路,更高带宽的芯片互联,并根据成本在不同的工艺节点上进行优化。