本文来自微信公众号“半导体行业观察”,作者/杜芹。

在当今数字化的时代,云计算的兴起、物联网设备的普及以及人工智能的使用,共同推动了全球数据量的爆炸式增长。据Statista预测,到2025年,全球每年将产生79 zettabytes的数据。这是什么概念呢?仅1 zettabyte的数据容量,就足以存储高达300亿部电影!为了跟上数据的快速增长,技术设计人员正在积极创新接口和存储技术,以支持更高的容量和性能。

在这样的背景下,芯片接口的角色变得愈发重要。作为芯片与外部世界沟通的桥梁,它不仅是芯片的核心组成部分,也是整个数据处理和通信过程的关键环节。随着需求的不断升级,我们见证了高速芯片接口技术的快速发展,主要表现在以下几个方面:首先,云计算系统对更快的数据传输速率的需求促成了PCIe 5.0和PCIe 6.0接口的发展,它们正在逐渐替代传统的PCIe 4.0接口;其次,存储设备和固态硬盘(SSD)正逐步转向采用PCIe 5.0/6.0接口;最后,数据中心也在向CXL 2.0接口过渡,以适应日益增长的数据处理需求。

然而,传统的芯片接口设计侧重性能和功耗优化,而忽视了安全性问题。近年来,系统复杂度不断提高,多芯片设计日益普及,其攻击面也随之扩大,硬件可能成为不法分子攻击的新目标。加之黑客的攻击手段不断升级,芯片接口安全问题已成为芯片设计和应用中亟待解决的重大挑战。

芯片安全新趋势:聚焦SoC接口安全

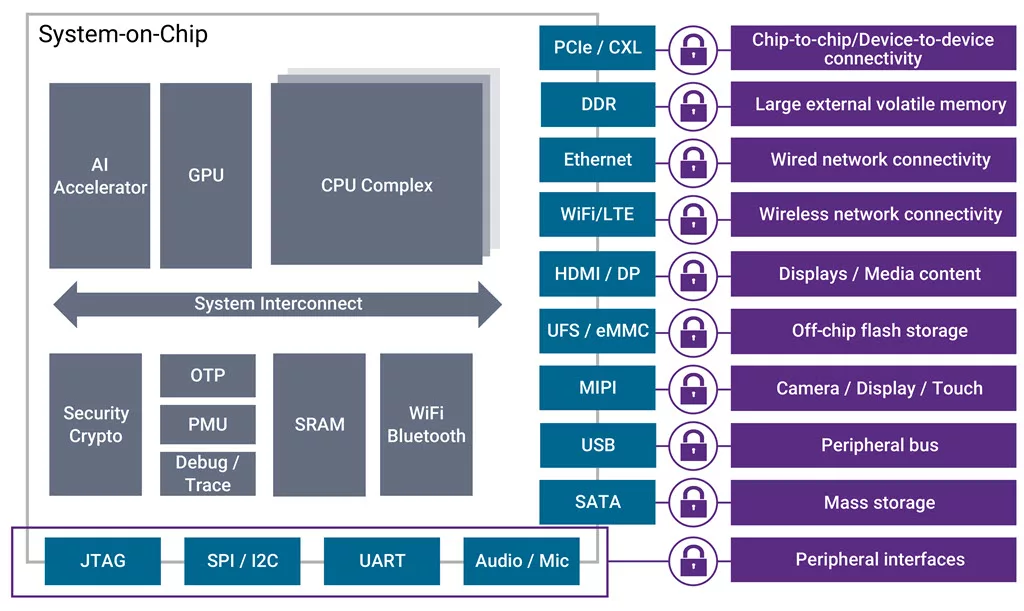

数据安全是推动互联世界发展的基石,也已成为芯片设计师和标准制定机构的首要焦点。在复杂的SoC设计中,众多关键接口如DDR、PCIe、CXL、以太网、MIPI、USB、UFS、eMMC、HDMI和DisplayPort,不仅是数据传输的枢纽,也可能成为攻击者利用的漏洞。因此,强化这些接口的安全性是提升SoC安全性的关键。

2020年,在PCIe和CXL标准中引入安全功能标志着对安全IP需求的显著增长,尤其在高性能计算应用领域更是如此。同时,自动驾驶汽车的兴起和汽车电气化所带来的安全挑战促使相关网络、ADAS摄像头/传感器连接和显示器规范进行适应性调整以应对这些新风险。

保障数据安全,就如同构筑一道坚不可摧的防线。如果将SoC比作是一个城堡,那么这些众多的接口就是城堡的众多“大门”。设计师们在SoC设计阶段就必须采取策略,保护这些“大门”,通过在它们上实施高级加密技术,仿佛为这些门加上了一层隐形的保护盾,即使遭遇不法分子的触碰,也难以被突破。这种方法对于保障整个系统的安全至关重要。

SoC有许多需要安全保护的接口

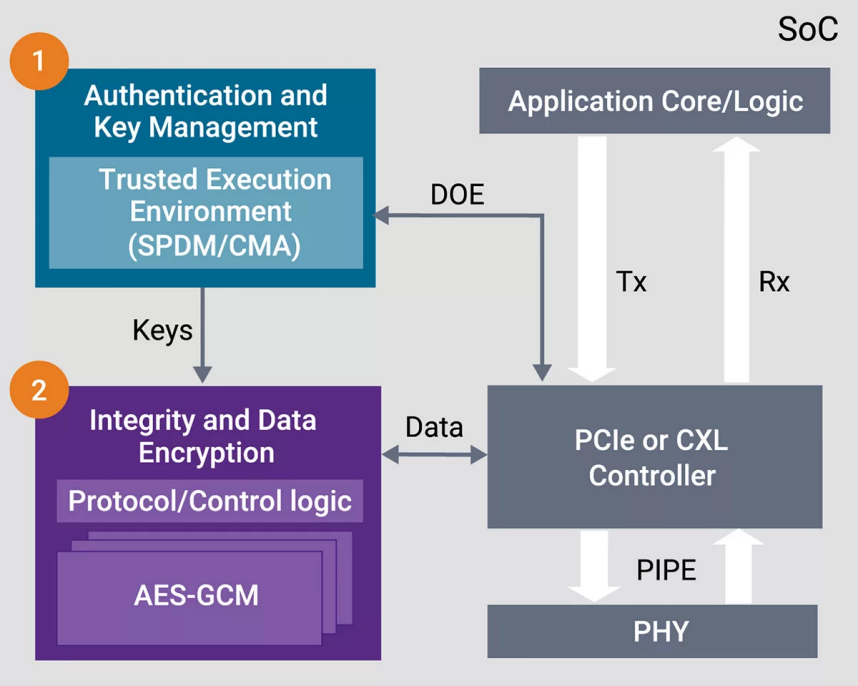

安全接口有两个必要的主要组成部分:第一部分是身份验证和密钥管理,就像是检查进出门的人是不是有钥匙的人;第二部分是完整性和数据加密(IDE),即在数据传输过程中保护数据不被篡改和窃取,就像是确保运送的东西在路上不被人偷看或偷走。这种保护不仅要保证数据安全,还要保证数据传输快低延迟。根据不同的门(接口)的类型,保护的方式和位置也不一样。比如PCIe和CXL这两种接口,它们的安全措施有点像,都需要身份验证和密钥管理,还要保证数据在传输过程中的安全。

PCIe和CXL安全系统级视图

除此以外,SoC设计人员在确保多种类型接口安全时,还需要考虑到额外的复杂性,因为各接口的标准日新月异。这些标准需要在不同层面上添加,这意味着协议可以在系统层面、控制器内部、物理层内部或物理层和控制器内部实施。

就算做到了遵守所有的规则和标准,设计师们还得确保整个系统都是安全的。安全性不仅仅是加密和解密那么简单,如果重要的配置信息或者钥匙泄露了,整个系统的安全都会受到威胁。

随着技术进步,威胁和攻击方式也在持续变化,这要求全球范围内(无论是特定地区还是全球层面)采用更加可靠、具有更强韧性的安全解决方案。此外,量子计算等新兴技术的出现将能够破解当前所有公钥基础设施算法,这意味着在未来5至10年乃至更长时间内,标准需要做出调整以纳入量子安全算法。

新思科技领跑安全接口创新,

发布最广泛的安全接口IP

为了支持SoC设计人员在高性能计算(HPC)、移动通讯、汽车技术和物联网(IoT)等领域迅速实现安全设计,新思科技紧随高速接口技术的发展趋势,推出了一系列安全接口IP解决方案。

(1)具有完整性和数据加密(IDE)功能的安全PCIe/CXL接口

首先是,随着数据中心、网络和移动设备对高性能互连的需求不断增长,PCIe和CXL已成为高速互联关键接口技术。为了保障数据安全,从2020年底的PCIe 5.0和CXL 2.0开始,到最新一代的PCIe 6.0和CXL 3.0,PCIe和CXL标准均引入了IDE安全功能,可防止数据篡改和链路物理攻击。

新思科技为PCIe和CXL提供经过硅验证的IP解决方案,具有高吞吐量、低延迟(CXL低至0周期)和高能效的特点,包括具有IDE安全性的控制器、物理层器件和验证IP。IDE安全模块采用适用于PCIe/CXL的新思科技控制器IP进行设计和验证,可加快SoC上市时间,同时提供适应设计特定用例所需的可配置性。目前,适用于PCIe 5.0/6.0或CXL 2.0的新思科技IDE安全模块IP已由超大规模云提供商部署。

新思科技PCIe IDE安全模块框图以及与PCIe控制器的集成

新思科技CXL IDE安全模块框图以及与CXL控制器的集成

(2)具有内联存储器加密(IME)功能的安全DDR/LPDDR接口

随着数据安全需求的不断增长,内存接口的安全防护也变得尤为重要。类似于发生在PCIe和CXL接口的完整性和数据加密(IDE)安全性措施,在DDR和LPDDR等内存接口中也看到了类似的发展轨迹。

一种常见的做法是将数据在发送到DDR控制器之前进行加密。然而,这种方法会导致性能下降和功耗增加,因为加密/解密操作需要额外的计算和存储资源。

新思科技所推出的具有内嵌存储器加密(IME)功能的安全DDR/LPDDR接口,其关键之道在于将加密/解密紧密耦合在DDR或LPDDR控制器内部,从而实现最大的内存效率和最低的总体延迟。

它具有以下优势:

它是一种基于AES-XTS算法的符合标准、可认证的开箱即用解决方案,可为内存控制器(包括新思科技Secure DDR5/4、LPDDR5X/5/4X或LPDDR5)提供高效吞吐量。

●支持AES-XTS的所有密钥大小,包括128位、256位密钥,并支持可扩展的128位、256位和512位数据路径。

●IME安全模块通过按地址或边带密钥选择为您提供按区域的内存保护,延迟非常低,并且可以针对具有最佳PPA的特定应用进行调整。

●新思科技Secure DDR5/4和LPDDR5X/5/4X/4控制器内部启用了内存加密,可节省用户的性能预算以更好地使用,并提供业界最低的延迟。

除了安全PCIe/CXL、DDR/LPDDR接口之外,新思科技还为最广泛使用的协议提供完整的符合标准的安全接口解决方案,如下图所示,包括采用介质访问控制安全(MACsec)的安全以太网接口、具有高清内容保护(HDCP v2.3)的安全HDMI和DisplayPort接口、具有加密和认证功能的安全USB接口、利用芯片到芯片接口加密确保多芯片系统安全、端到端安全传输的安全MIPI接口、具有内联加密和高级重放保护内存块(RPMB)功能的安全UFS和eMMC接口。这些安全接口提供了预先验证的解决方案,并与控制器集成,以满足最广泛使用的协议标准,同时兼顾性能、延迟和面积等关键指标。这些解决方案将帮助设计人员降低风险,加快产品上市时间。

新思科技为最广泛使用的协议提供安全接口

结语

综上所述,将安全性整合进SoC设计是一项必不可少的任务,并将持续受到互联应用、法律法规及标准演变的影响。所有接口,包括MIPI、VESA和UCIe,都在更加积极地采纳安全措施。使用新思科技的安全接口IP解决方案,有助于抵御互联设备中不断演变的各种威胁,例如盗窃、篡改、侧信道攻击、恶意软件和数据泄露,帮助设计人员在互联时代构建更加可靠、可信的系统。