本文来自微信公众号“中国电子报”,作者/沈丛。

AI快速走热的这一年多来,不断增长的算力需求对本就陷入瓶颈的芯片制程技术带来了挑战。微缩工艺可以通过不断缩小晶体管尺寸来提高芯片集成度和性能,但随着制程技术越来越接近物理极限,微缩工艺的发展空间越来越小。Chiplet等先进封装技术,可以通过将多个芯片集成在一起提高算力和性能,同时还可以降低成本和功耗。因此,在AI时代,先进封装技术越来越受到关注。未来,芯片制程技术需要在微缩工艺和先进封装之间取得平衡,以满足不断增长的算力需求。

自2012年以来,深度学习被广泛应用,AI算法的网络结构持续高速增长,单一AI算法对算力的需求增加了30万倍。高速扩张的算力需求,使多次被预言放缓乃至完结的摩尔定律,重新获得了生命力。台积电(中国)有限公司副总经理陈平在日前举办的2023中国临港国际半导体大会上表示,随着对算力的需求越来越高,业内对先进制程芯片越发热衷。

OpenAI CEO奥特曼曾预测,对于AI时代的摩尔定律来说,集成电路上可以容纳的晶体管数目在大约每18个月会增加一倍。其发展周期与此前摩尔定律中的18~24个月相比,略微超前。随着AI时代的到来,摩尔定律的演进反而有所提速。

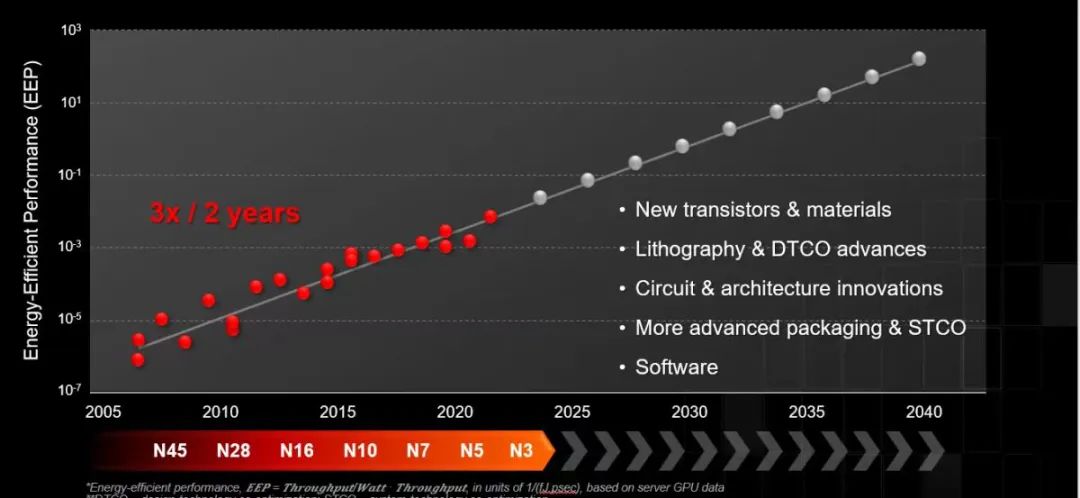

陈平认为,在关注芯片制程缩小的同时,也要关注芯片的算力和能效比,包括新型晶体管和材料、光刻技术和DTCO(设计与工艺协同优化)的进步、电路和架构的创新、先进封装和STCO(系统工艺协同优化)以及软件优化等。这些因素的协同作用将推动半导体技术的不断进步,实现更高性能、更低功耗和高能效比的芯片设计。

半导体制程技术演进的动力——算力和能效比

图片来源:台积电

中国半导体行业协会集成电路设计分会理事长、清华大学教授魏少军认为,除了缩小芯片制程外,还可以利用三维混合键合技术对存储器晶圆和逻辑电路晶圆进行异质集成,从而提升芯片的算力。这种集成方式对于逻辑电路的晶圆没有代工厂及工艺节点的限制要求,具有更高的灵活性和适应性。而存储器晶圆由DRAM晶圆厂制造,保证了存储器的品质和性能。混合键合晶圆加工则在晶圆代工厂制造完成,实现了工艺的高效整合。这种集成方式将不同工艺的晶圆优势结合起来,提升了芯片的性能和功能,满足了人工智能等领域对于高算力和低能耗的需求。

魏少军认为,为了增强芯片的灵活度,实现算力的合理分配,还可以将软件定义芯片与异质堆叠集成相结合,构建软件定义近存计算芯片技术。软件定义芯片是一种先进的芯片设计技术,通过将任务处理空间并行化,实现硬件资源的时分复用,从而提高了芯片的处理效率和性能。而异质堆叠集成技术则通过将存储单元和计算单元紧密集成在一起,缩短了数据传输距离,降低了数据传输能耗,进一步提升了芯片的性能。这种技术能够更好地满足AI时代对算力和能效比的要求,同时也提高了芯片的安全性。

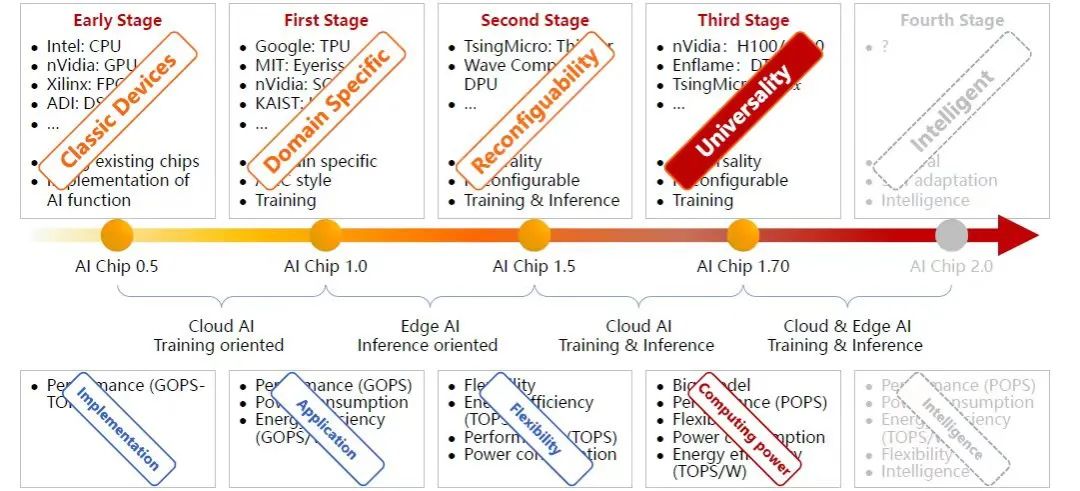

人工智能芯片的主流架构演进图

来源:清华大学

在人工智能的蓬勃发展下,Chiplet逐渐崭露头角,备受业界瞩目。中国半导体行业协会副秘书长兼封测分会秘书长徐冬梅指出,由于人工智能和HPC高性能计算领域需要处理大规模数据和复杂计算,对芯片设计规模的要求极高,因此这两个领域对于Chiplet技术的需求更为迫切。

随着ChatGPT等高普及度的AI技术不断发展,其背后的芯片需求也日益旺盛。数据显示,到2024年,Chiplet芯片的全球市场规模将达到58亿美元,2035年将达到570亿美元,显示出Chiplet市场的巨大潜力和增长空间。尽管Chiplet技术的发展前景看好,但它并不能完全取代先进制程技术。对此,陈平表示,尽管通过Chiplet将几个芯片组合在一起可以扩展芯片的功能,但这种组合方式并不能完全取代先进制程技术。Chiplet虽然能够实现更复杂的计算和数据处理能力,但并不能改变芯片的品质,也就是能效比和算力密度。因此,在业界追求更高性能和更低能耗的过程中,仍需要不断提升芯片制程,与Chiplet互补提升。