本文来自半导体产业纵横,作者/刘浩磊。

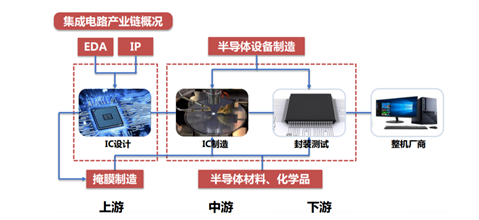

EDA软件作为关键的芯片设计工具,是集成电路产业的一大基石,随着国内芯片产业链的不断深入,大众对于上游EDA的关注度也直线上升。

EDA(Electronic Design Automation,电子设计自动化)软件作为关键的芯片设计工具,是集成电路产业的一大基石,随着国内芯片产业链的不断深入,大众对于上游EDA的关注度也直线上升。EDA技术经过多年发展,产品功能及丰富度不断提高,目前EDA工具已能对集成电路的设计、制造、封装等环节实现全覆盖。EDA对现代集成电路产业意义重大,它不仅极大地降低了芯片的设计成本,使大规模的复杂电路设计成为现实,同时也推动了IP生态的丰富,EDA技术与现代先进工艺的结合更是为集成电路性能提升、尺寸缩减带来新的发展机遇。在未来,云和AI技术将在EDA领域持续渗透,目前海外EDA巨头已开始布局有关产品,EDA在效率、性能上有望进一步提升。

四大发展历程

EDA是指利用计算机辅助设计软件完成超大规模集成电路芯片的功能设计、综合、验证等流程的设计方式。

随着集成电路产业的发展,设计规模越来越大,制造工艺越来越复杂,设计师依靠手工难以完成相关工作,必须依靠EDA工具完成电路设计、版图设计、版图验证、性能分析等工作,EDA产业渗透率逐渐提高。随着超大规模集成电路的持续发展,晶体管密度快速上升,芯片设计难度持续加大,加上工艺变革的加快,电子工程师更加需要利用EDA工具来提升逻辑综合、布局布线、仿真验证的效率,EDA作为集成电路上游设计的基础工具,逐渐成为了刚需。

EDA作为芯片设计的基石,其发展大致经历了四个阶段,目前已在计算机、通信、航天航空等领域发挥着重要作用。

(1)计算机辅助设计(CAD)阶段:在20世纪70年代以前,设计人员依靠手工完成电路图的输入、布局和布线。到了70年代中期,可编程逻辑技术出现,开发人员尝试实现整个设计工程的自动化,而不仅仅满足于自动完成掩膜草图,这是EDA的雏形时期。

(2)计算机辅助工程(CAE)阶段:随着超大规模集成电路的发展,电子系统变得更为复杂,语言编程开始应用于芯片设计。在80年代出现了硬件描述语言VHDL和Verilog,为EDA的商业化奠定了基础。

(3)电子系统设计自动化(EDA)阶段:硬件语言趋于标准化以及芯片设计技术在不断丰富,EDA设计工具快速普及和发展,这一阶段也是EDA发展的黄金期。设计手段包括全定制设计、半定制设计、ASIC设计、标准单元库、门阵列、可编程逻辑阵列等。

(4)现代EDA技术:21世纪后,EDA技术快速发展,软件效率显著提升,仿真验证和设计两层面的EDA软件工具功能更加强大,更大规模的可编程逻辑器件不断推出,系统级、行为级硬件描述语言趋于更加高效和简单。

被美国企业牢牢掌握的EDA话语权

经过不断的市场洗牌,EDA行业已经成为一个高度垄断的行业,国际三巨头企业占据绝对主导地位。

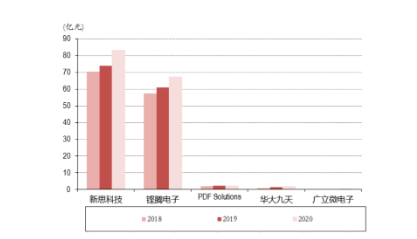

经过30余年的发展整合,全球EDA市场主要由新思科技(Synopsys)、铿腾电子(Cadence)及西门子EDA(Mentor Graphics,2021年更名为Siemens EDA)垄断,共占据了全球约78%的市场份额。三家公司均具有完整且优势突出的全流程产品线,并且在部分领域拥有绝对优势,如新思科技在逻辑综合工具及时序分析工具上具有绝对优势,西门子EDA在各类布线工具上优势显著。

在近年来全球集成电路产业基本保持稳定向好的发展态势下,近年全球EDA工具总销售额保持稳定上涨,2020年实现总销售额72.3亿美元,同比增长10.7%。根据赛迪智库统计,在2020年全球各地区EDA市场销售额方面,北美约占40.9%,亚太地区约占42.1%,欧洲地区约占17%。目前北美地区是EDA技术最为发达的地区,而中国大陆地区集成电路设计业的快速发展带动了亚太地区EDA工具销售额的增长。

国内EDA产业发展之路与现状

国内EDA行业先后历经“封锁、集中突破、国产遇冷、再启动、发展提速”五个阶段,当前与全球领先EDA软件仍存在差距。

(1)封锁:1950~1986年,20世纪70至80年代,由于巴黎统筹委员会对中国实施的禁运管制,西方全面封锁技术,国外EDA无法进入国内市场,在八十年代中后期,国内开始投入EDA领域的研发;

(2)集中突破:1986~1994年,国家组织资源在北京成立研发中心开发EDA软件,1993年了中国历史上第一款具有自主知识产权的EDA工具国产“熊猫ICCAD系统”诞生,填补了我国在这一领域的空白,打破了西方封锁;

(3)国产EDA遇冷:1994-2008年,由于国外解除了对我国EDA工具的封锁,国内大量购入成熟EDA软件,Cadence、Synopsys等EDA企业进入中国,国产EDA遇冷,缺少政策和市场支持的国内EDA工具研发和应用陷入低谷,这种情形也导致了国内集成电路产业对国外EDA工具的重度依赖;

(4)再启动:2008-2018年,EDA列入国家“核高基”重大科技专项,重新获得了鼓励和扶持;华大九天成立,承担EDA核高基任务;

(5)发展提速:2018年至今,国产EDA处于发展提速期,大基金领头投资国产EDA龙头企业华大九天;此外华为受到美国制裁,EDA受限,国内对其重视程度提升;“国发8号文”将设计工具作为突破重点。

历经几十年的发展,目前国产EDA企业代表包括华大九天、国微集团、芯华章、广立微、概伦电子、芯和半导体等。而国内外EDA软件多年累积的技术差距难以在短时间内抹平,在全流程的EDA平台、产业链生态等方面,国内企业和海外厂商还有着一定的差距。

由于我国EDA行业发展过程曲折,当前海外EDA巨头在全球范围能仍全面领先本土EDA企业,差距主要体现在研发及技术、渠道及产品、生态及客户关系这三方面。

EDA作为高技术壁垒的行业,企业唯有投入大量的研发资源并获取顶尖人才的贡献才能保持竞争力。当前,中外厂商在研发投入方面差距巨大,以华大九天和新思科技为例对比,新思科技2018-2020年三年累计研发投入228亿元人民币,是华大九天近60倍。此外,海外三巨头在发展过程中累计并购各类公司200次以上,其中Synopsys次数高达80次。正是通过不断地兼并和收购,三家公司不断扩张自身的业务和产品线边界,规模快速扩大。国内EDA企业难以效仿。

海外企业经年累月的大量研发投入使得其在产品线丰富度、渠道多样性上领先于国内EDA企业。目前我国EDA企业在局部环节具有优势,如华大九天的模拟电路仿真、概伦电子的SPICE建模领域等,但在产品丰富度上仍逊色于海外巨头。

相比于国内EDA企业,海外EDA巨头拥有完整的EDA产品线、工具链以及丰富的IP库,通过为客户提供丰富多样、具有自主知识产权的IP核,而IP授权对于Fabless客户的研发是不可或缺的,进一步提升了客户黏性,从而构建具有深度护城河的生态圈。此外国内厂商缺乏与头部Foundry的深度合作,国产EDA产品难以匹配最先进的工艺,这也导致本土企业难以进入高端芯片设计领域。

2019年以来,美国对我国国内高科技企业的制裁力度不断加大,数次提高对国内部分高科技企业的限制级别,尤其在集成电路和EDA工具领域体现的较为明显。例如,2019年EDA三巨头终止了与华为海思的合作,为国产芯片的发展蒙上了一层阴影。国内集成电路设计及制造企业开始寻求实现EDA工具软件的进口替代。对于国内EDA厂商而言,这是一个化危为机的重要时刻。

EDA未来发展趋势

随着晶圆制造工艺接近物理极限,摩尔定律正逐步放缓,集成电路产业开始注重从更多维度提升电子系统性能和功能复杂度。在后摩尔时代技术从单芯片的集成规模、功能集成、工艺、材料等方面的演进驱动着EDA技术的进步和其应用的延伸拓展。

EDA+云

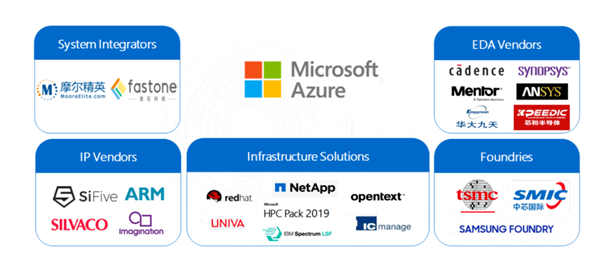

过去安全隐患是阻碍IC设计上云的关键问题,近些年来,伴随着弹性算力、安全等相关技术的逐渐成熟,市场参与者准备就绪、用户使用习惯改善,IC设计上云不再像多年前那样只是个简单的口号,“云计算+EDA工具”的模式开始逐渐得到认可。此外国际贸易大环境,令半导体产业向中国国内偏移,芯片设计市场竞争加剧,这些因素进一步促成IC设计上云。

早在2020年微软就与Mentor Graphics、台积电、AMD多方合作,在微软云Azure上验证了7nm的芯片设计,其中,在同Mentor的合作过程中,Mentor的AMS使用了微软云Azure专门针对HPC开发的虚拟机类型HC44rs,每个核心有8GB的内存来调用,大幅度缩短EDA的过程,提升效率加速产品上市。

此外,Synopsys与三星合作推出了SAFE云设计平台,共同为Samsung Foundry的客户提供可拓展的安全的云端设计环境,在该环境中可实现IC设计和验证、全数字和模拟流程。

而中国目前的芯片设计企业,多数是规模在100人以下的小型企业。这些中小企业的痛点在于人才、设计能力缺乏,以及基础设施跟不上。与此同时由于竞争的加剧,要求企业以更快的速度将芯片产品推向市场。EDA上云恰好能够解决这些问题,包括算力的充沛及弹性供给,IT基础设施、CAD皆准备就绪,加上更多EDA、IP、Foundry相关资源的整合,为中小型芯片设计企业提供了天然解决固有痛点的平台,时间与成本都得到极大程度的降低。

EDA+人工智能

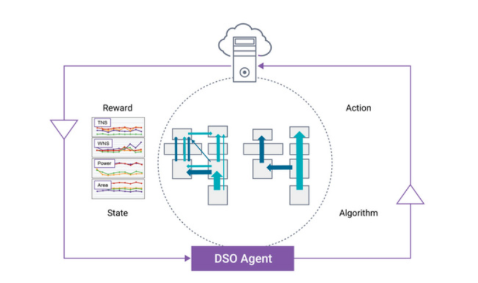

近年来芯片复杂度持续提升使得设计基础数据规模不断增加,其对系统运算能力需求有跃迁式提升,AI将更好地实现EDA设计中算力、资源的分配,因此人工智能赋能EDA技术势在必行。

具备AI特性的EDA工具可以大幅提高设计效率,缩短芯片设计周期,厂商借助AI算法可实现EDA数据训练以提升产品质量。

例如,2020年3月11日Synopsys推出了业界首个用于芯片设计的自主人工智能应用程序DSO.aiTM(设计空间优化AI),通过搜索大规模扩展设计空间优化解决方案,利用强化学习来提高功率、性能和面积,缩短交付时间,并通过自动化降低总体开销。

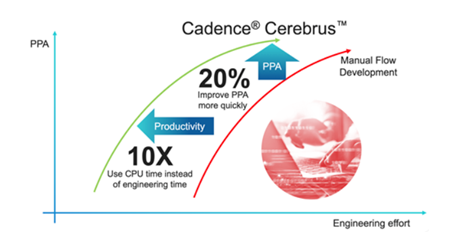

Cadence于2021年7月推出基于机器学习的设计工具Cerebrus,与人工方法相比,将工程生产力提高多达10倍,同时最多可将功耗、性能和面积结果改善20%,以快速满足包括消费电子、超大规模计算、5G通信、汽车和移动等广泛市场的设计要求。该产品已被瑞萨电子和三星使用。

后摩尔时代下日益繁复的芯片设计给EDA产品带来挑战的同时,也为技术迭代打开了一扇全新的机遇之窗。随着我国相关利好政策的推进,新兴技术的逐渐成熟,国内EDA企业迎来新的发展机会。尽管打破海外EDA企业的壁垒困难重重,但仍值得期待。