本文来自微信公众号“半导体产业纵横”,编译自semiengineering。

晶圆上芯片3D堆叠最大限度地缩短了硅和光子集成电路之间的互连距离。

随着我们进入人工智能时代,对云服务和人工智能计算增强连接的需求不断激增。随着摩尔定律的放缓,不断增长的数据速率要求正在超越任何单一半导体技术的进步。这种转变凸显了异构集成(HI)作为缓解带宽瓶颈的关键解决方案的重要性。如今,OSAT(外包半导体组装和测试)不仅受到先进节点IC封装需求的推动,还受到硅光子学和共封装光学等新兴技术兴起的推动。ASE推出了硅光子封装平台,旨在提供创新解决方案,以促进更先进的人工智能系统,同时确保高性能和能效。

需要提高计算性能并提高能源效率

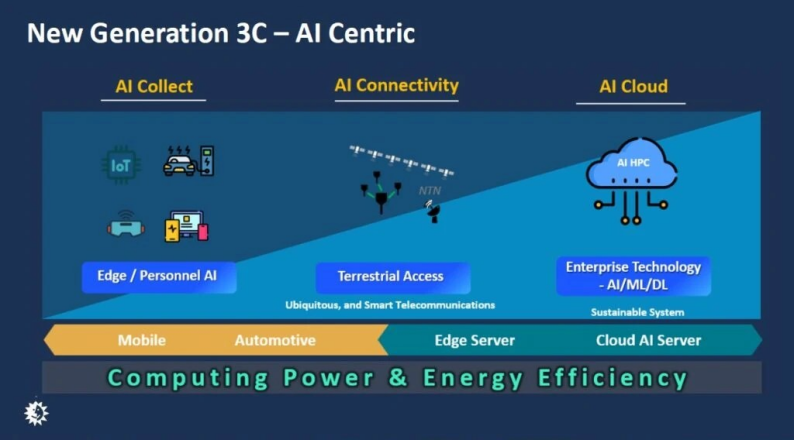

在快速发展的人工智能领域,当前的训练周期取决于三个核心过程:数据收集、数据连接以及利用高性能计算(HPC)进行人工智能训练和推理。

随着AI应用日益复杂,现有的硬件架构往往难以实现更高的计算性能,同时提升跨芯片和I/O数据连接的能源效率。

用于AI芯片集成的先进封装

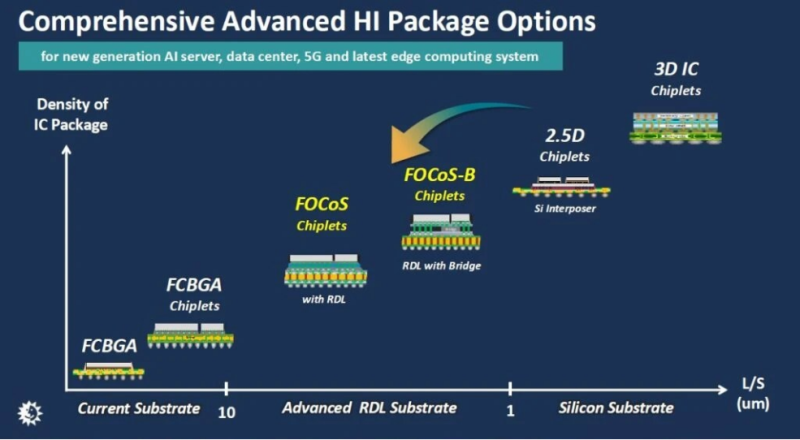

AI硬件的首次演进侧重于使用先进的HI封装来集成来自不同晶圆节点的芯片,尤其是用于集成逻辑和内存。ASE提供高密度封装解决方案,旨在满足AI和HPC应用对更高带宽和更快数据传输速率日益增长的需求。我们的产品包括2.5D和3D IC、扇出型基板芯片(FOCoS)和FOCoS-Bridge。

2.5D封装技术利用Si Interposer上的重分布层(RDL)连接芯片,实现了低至0.5μm/0.5μm的显著线宽/线间距(L/S),使其成为高性能应用的理想选择。FOCoS利用扇出型RDL无缝集成各种芯片,提供L/S范围从2μm/2μm到10μm/10μm的经济高效的解决方案。最后,FOCoS-Bridge采用硅桥来促进高密度布线,以在需要高速传输的区域连接不同的芯片(例如逻辑芯片和内存芯片),同时还在其他区域使用扇出型RDL。这种方法为L/S设计提供了灵活性,提供0.5μm/0.5μm和2μm/2μm选项,同时显著提高封装密度和带宽。

利用光子系统集成推动人工智能发展

高密度封装解决方案可以实现更高的I/O密度,并显著减少AI芯片之间的互连距离,通常涉及约10个芯片。这可以实现更紧凑的设计,可将系统尺寸缩小高达70%,同时将整体计算性能提高高达10倍。从长远来看,我们认为理想的封装解决方案将涉及利用全尺寸晶圆作为单个封装设备。

要达到ExaFLOPS的计算能力,至少需要1,000个AI芯片通过先进的高密度RDL技术进行互连。未来将出现包含数百万个芯片的AI集群,用于复杂的AI训练模型,这将需要一种更有效的系统级连接方法。

与电互连相比,光互连的传输损耗明显更低,这使得光子集成成为未来AI系统开发的一个有前途的解决方案。业界正在见证各种国际项目,例如欧洲的photonixFAB、美国的DARPA计划和日本的IOWN全球论坛,这些项目旨在扩展I/O功能,同时提高带宽并降低功耗。它们都专注于一种类似的方法,即共封装光学(CPO)。

共封装光学元件(CPO)的复杂组装过程

CPO正在成为未来AI硬件的一项赋能技术,主要用于连接AI集群中的服务器。在典型的CPO网络配置中,交换机ASIC位于中心位置,周围环绕着多个光子引擎(也称为光学引擎或OE)。

CPO组装涉及各种元件,包括激光器、光学元件、光纤阵列单元(FAU)和具有不同晶圆节点的硅集成电路(IC):光子集成电路(PIC)、电子集成电路(EIC)和存储器IC。一些客户需要专门的CMOS后晶圆工艺,例如深反应离子蚀刻(DRIE)腔体形成、AuSn键合、KOH V型槽或扇出RDL工艺。

最终,所有上述元件都集成在单个封装基板上,然后进行最终测试。这导致组装流程非常复杂,如下图所示。关键工艺—EIC/PIC 3D集成和光纤组装。

用于CPO中EIC/PIC集成的先进封装

对于EIC和PIC的集成,晶圆上芯片3D堆叠是一种有效的方法,可以最大限度地缩短两者之间的互连距离。这种方法具有尺寸更小的优点,同时显著提高了带宽密度和能效。两种主要方法有助于实现垂直互连:硅通孔(TSV)和扇出型封装(FOPOP)配置中的高铜柱。

选项1:PIC位于EIC之上

在此配置中,PIC位于EIC顶部。然而,在EIC中创建TSV可能具有挑战性,因为它通常需要在先进的晶圆节点上制造。为了克服这个问题,我们采用了晶圆级扇出工艺,形成高铜柱以实现与顶部PIC的垂直互连。由此产生的光子FOPOP在光耦合方面表现出色,因为PIC的悬垂部分允许光边缘耦合。

选项2:PIC位于底部

或者,PIC可以位于底部,使用其中形成的TSV与顶部EIC进行垂直互连。FAU组装解决方案以及PIC翘曲控制对于这种光子无模2.5D结构至关重要。由于更好的电源完整性和信号完整性,这种设计提供了更好的散热效果,并且可以实现更高的传输数据速率,例如每通道超过200G。

最终,光子无模2.5D结构提供了卓越的解决方案,使得带有TSV的PIC成为硅光子学不可或缺的一部分。

光纤到PIC组装解决方案

对于光纤到PIC集成,有几个关键考虑因素:主动对准、被动对准、边缘耦合和光栅耦合。

为了实现更好的光学性能(最大限度地减少光损耗和波长敏感度),笔者认为使用透镜进行主动对准的边缘耦合是最佳选择。然而,考虑到对晶圆级光学可测试性的需求,晶圆级解决方案(例如使用被动对准的晶圆上芯片镜耦合器)可能更适合大批量生产。

因此,业界正转向晶圆级组装,在大批量CPO制造中利用垂直耦合器进行光学和FAU组装。这些耦合器可以扩大激光束尺寸,提供更大的耦合公差。这种方法允许进行晶圆级测试,支持可拆卸的FAU,并且对波长变化不太敏感,最终支持密集波分复用(DWDM)系统。

构建协同生态系统

在探索AI硬件开发这一复杂领域时,在系统集成商、设计公司、代工厂和OSAT(外包半导体组装和测试)提供商之间建立协同生态系统至关重要。成功的关键在于明确定义规范并开发可简化整个供应链的已知良好光学引擎(OE)解决方案。AI硬件的未来充满希望,通过优先考虑性能、能源效率和创新的封装解决方案,可以释放AI技术的全部潜力,为更智能、更高效的世界铺平道路。