本文来自微信公众号“半导体行业观察”。

内存计算(CiM)已成为一种有吸引力的计算范例,可解决深度学习应用传统设计中的内存和电源墙问题。借助CiM,运行深度学习算法所需的部分计算可以在内存本身中执行,从而避免在内存和处理单元之间移动大量数据。

在深度学习算法中,主要运算是权重矩阵和输入向量的矩阵向量乘法。在这些操作中,来自输入向量的激活信号乘以预编程的权重,这些权重存储在存储器元件的阵列中。输出是求和线(或位线)上所有贡献的加权和。

正在研究用于存储权重的不同类型的非易失性存储器技术。最流行的是电阻式存储器,例如电阻式RAM(RRAM)、相变存储器(PCM)和磁性RAM(MRAM)——存在两种不同电阻状态的存储器。存储元件排列成交叉阵列并将权重存储为电导。

几年前,佐治亚理工学院的研究人员开始探索在模拟CiM应用中使用铁电电容器(FeCAP)存储重量的可能性。与电阻式存储器相比,FeCAP具有两大优势:(1)电路显着提高了功率效率,(2)由于没有潜行电流流过电路,因此无需选择器器件。

需要非破坏性读取操作

FeCAP类似于传统电容器,但在两个金属层(电极)之间具有铁电材料,而不是传统的介电材料。铁电材料可以存在两种电极化状态-P+和P--可以通过外部电场反转。当该场被移除时,铁电材料保持其极化状态,从而使FeCAP具有非易失性特性。

如今,铪锆氧化物(HZO)因其具有缩放潜力而成为存储器应用的首选铁电材料。然而,读取HZO基FeCAP偏振态的传统方案具有破坏性:它依赖于铁电材料的偏振切换,因此需要在每次读取操作后重新编程偏振态。因此,数据读取操作的最大数量(即,读取耐久性)与数据写入操作的最大数量(写入耐久性)相关联。因此,读取耐久性无法独立优化。这对于CiM应用程序来说是一个问题,因为它需要几乎无限的读取耐久性,而低得多的写入耐久性通常就足够了。

FeCAP具有>10 11无损读取耐久性和~8.7电容存储窗口(0V时)

在2023年IEDM会议上,imec和佐治亚理工学院首次提出了一种将FeCAP的读写耐久性完全解耦的解决方案。该解决方案基于在两个电极的界面中引入不对称性。这些非对称设计的FeCAP器件可以被读出超过1011次,而不会干扰HZO铁电体的极化状态。此外,在0V读取电压下获得了创纪录的8.7的电容存储窗口,代表了P+和P-态铁电体相对介电常数之间的差异。这些结果使FeCAP成为CiM应用前景广阔的技术。

非破坏性读取操作背后的机制

非破坏性地读出具有>1011耐久性的FeCAP的能力部分是通过研究读出机制背后的物理原理实现的。对基本原理的基本理解也为进一步改进结果提供了坚实的基础。

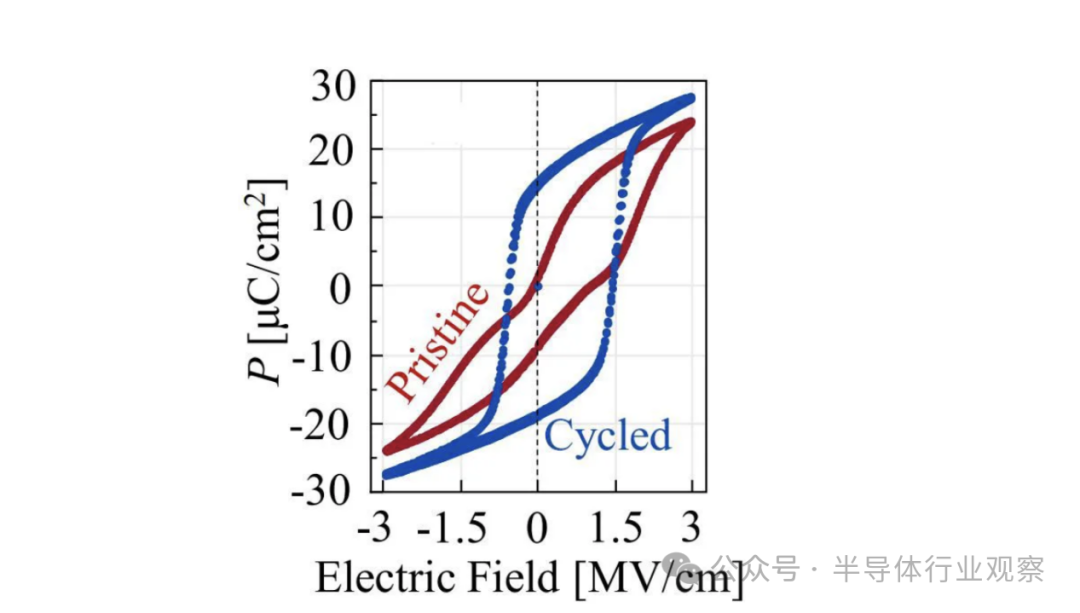

与传统介电材料不同,铁电材料在施加的电场和极化电荷之间具有非线性关系,从而使铁电极化电压(PV)特性呈现磁滞回线的形式。

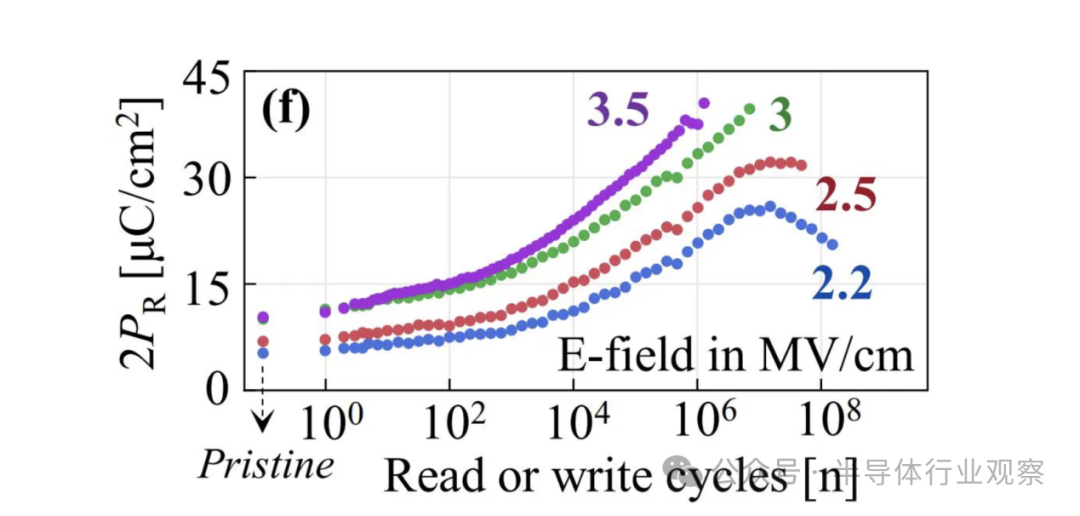

这种现象被用于FeCAP的传统读取方案中。实际上,施加电压脉冲以将存储单元翻转到其相反的极化状态。当这种情况发生时,等于P+和P-之间的差值的位移电荷被释放并被检测到。这种差异称为剩余极化(2PR),代表记忆窗口。为了充分区分P+和P-,残余极化2PR在存储器的整个寿命期间应尽可能高。然而,主要缺点是每次读出后都需要对单元重新编程,使得读取耐久性取决于写入耐久性。

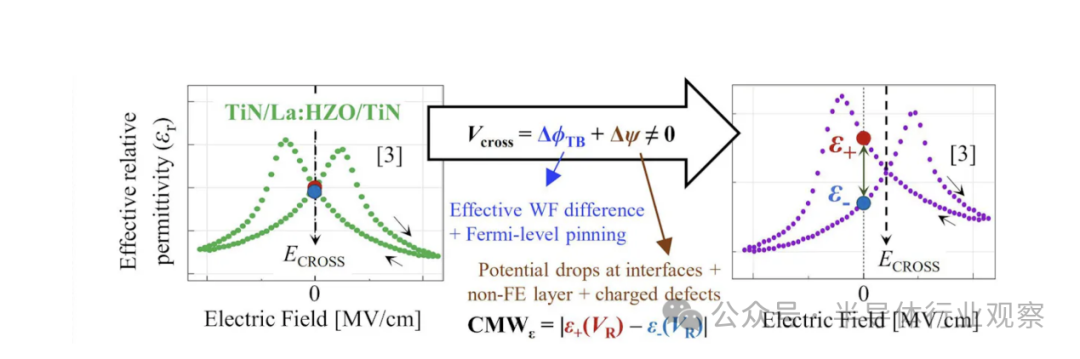

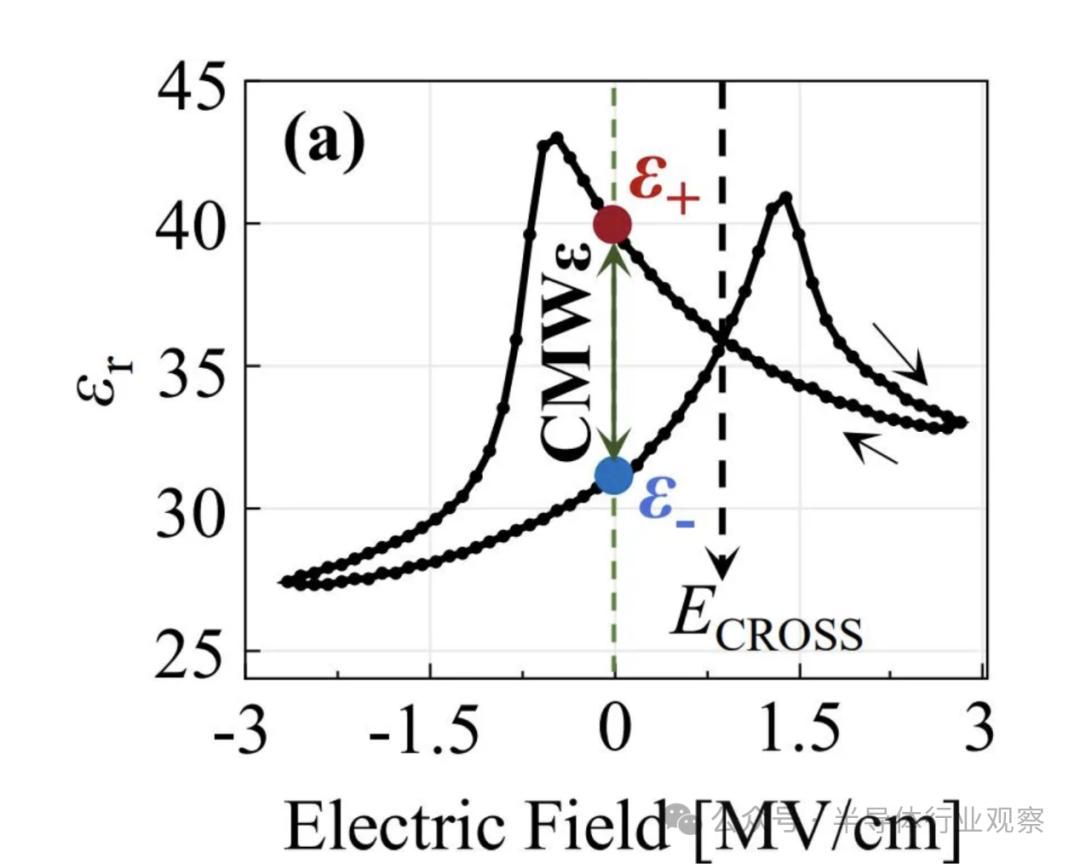

佐治亚理工学院和imec的研究人员采取了不同的方法。他们从不同的内存窗口概念开始。他们没有利用P+和P-之间的差异,而是使用电容内存窗口的概念。该电容存储窗口是FeCAP处于P+或P-状态时的电容状态之间的差异。它可以从CV测量中得出,CV测量绘制铁电材料对施加电场的非线性电容响应(或相对介电常数(εR))。

铁电电容器的CV曲线类似于0V附近的对称蝴蝶曲线,如图4的左侧部分所示。在0V(或零电场)下,蝴蝶曲线的正分支和负分支交叉,导致零电压电容存储窗口。但是,研究团队找到了一种通过对两个电极应用功函数差异来打开0V存储窗口的方法(参见图4的右侧部分)。经过电极的界面工程和材料堆叠的进一步优化后,在0V电压下可以获得高达~8.7的电容存储窗口。

然而,应用准静态CV测量来读出FeCAP并不是一种电路友好的读取操作。最后一步,研究人员表明,可以通过应用基于脉冲的读取方案并读出电荷来检索相同的信息,这在内存操作中更常用。通过这种读取方案,他们在0V DC偏压下实现了>1011个周期的非破坏性读取耐久性,而无需施加极化切换的电场(即矫顽场)。该方案允许读取耐久性与写入耐久性完全解耦。

展望:将应用领域拓展至FeRAM;迈向3D铁电存储器

目前正在进行研究,以进一步提高CiM应用的FeCAP的读取耐久性和电容存储窗口。这是通过进一步设计电极的材料堆栈和功函数来实现的。通过在非零直流偏置之上施加交流读取脉冲,还可以进一步扩大电容存储器窗口。然而,在这种情况下,必须注意不要超过矫顽场。

此外,imec的研究人员正在研究在类DRAM FeRAM存储器应用(嵌入式和独立式)中使用FeCAP和无损读出方案的可行性。然而,经典主动存储器和CiM类型操作之间存在一些显着差异。例如,对于主动存储器应用,除了高读取耐久性之外,还需要比CiM操作更高的写入耐久性。此外,在CiM中,在测量结果之前会累加同一位线上所有存储单元(小信号)的贡献。然而,在经典的存储器应用中,必须可靠地测量每个单独单元的状态。这对每个单独的FeCAP的读出信号的幅度提出了更严格的要求,需要更大的存储窗口。该团队正在探索FeRAM应用的规范以及如何实现它们。

对于这两种应用,预期趋势是进入第三维度以进一步增加存储密度。因此,通过可用于基于HZO的电容器的原子层沉积工艺,FeCAP将从平面电容器结构转变为3D电容器结构。从长远来看,基于FeCAP的存储器可以集成在外围逻辑电路之上。所提出的工艺技术的两个特征使这成为可能。首先,如前所述,由于不存在潜行电流,因此不需要选择器器件(通常是晶体管)。这使得能够将铁电存储器嵌入逻辑电路的后端(BEOL)中。其次,制造基于HZO的FeCAP(例如低温ALD工艺)所需的热预算低于400°C,使得该技术完全兼容BEOL。

imec和佐治亚理工学院的研究人员首次证明了以非破坏性方式读取FeCAP的可行性,从而完全解耦读写耐久性。可以证明非破坏性读取耐久性>1011,而写入耐久性约为107。读出机制基于电容存储窗口的概念,可以证明该窗口的记录高值为8.7。这些结果使FeCAP有希望成为CiM应用的候选者。此外,这些创新为探索FeCAP在嵌入式和独立FeRAM存储器应用中的潜力奠定了基础。