本文来自微信公众号“半导体产业纵横(ID:ICVIEWS)”,编译自semiengineering。

制造具有良好良率的可靠3D DRAM堆叠复杂且昂贵。

随着先进的人工智能加速器、图形处理单元和高性能计算应用需要快速处理的数据量持续激增,HBM的销量也在飙升。

受开发和改进大型语言模型(如ChatGPT)的巨大努力和投资推动,HBM库存已售罄。HBM是存储创建这些模型所需大部分数据的首选内存,而通过增加更多层来提高密度以及SRAM扩展的局限性,正在为这一热潮火上浇油。

Rambus硅知识产权部门高级副总裁兼总经理尼拉杰·帕利瓦尔表示:“大型语言模型(LLM)现在超过万亿个参数并持续增长,克服内存带宽和容量的瓶颈对于满足人工智能训练和推理的实时性能要求至关重要。”

这一势头得益于先进封装技术,它在许多情况下可以提供比平面系统级芯片(SoC)更短、更快、更稳健的数据路径。ASE投资者关系负责人肯·向在最近的一次财报电话会议上表示:“前沿封装技术正在蓬勃发展。无论是人工智能、网络还是其他正在研发的产品,我们对先进互连技术及其各种形式的需求看起来都极具前景。”

这正是HBM恰如其分地发挥作用的地方。三星电子DRAM产品规划副总裁兼负责人金仁东在最近的一次演讲中表示:“HBM架构将迎来一波大浪潮——定制HBM。人工智能基础设施的普及需要极高的效率和扩展能力,我们与主要客户一致认为,基于HBM的人工智能定制将是关键一步。功耗、性能和面积(PPA)是人工智能解决方案的关键,而定制将在PPA方面提供巨大价值。”

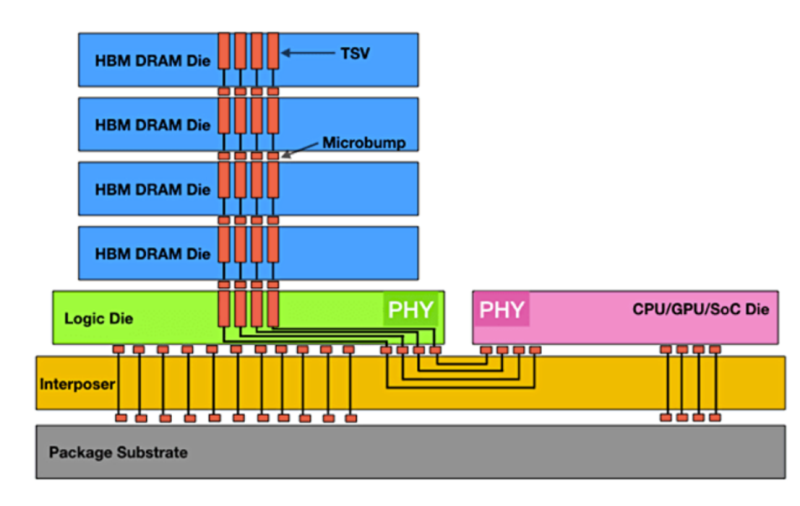

过去,经济因素严重限制了HBM的广泛应用。硅中介层价格昂贵,而在前端生产线(FEOL)工厂中处理大量穿透硅通孔(TSV)的成本也很高。ASE工程和技术营销高级总监李红曹表示:“随着高性能计算(HPC)、人工智能和机器学习的需求增加,中介层的尺寸显著增加。高成本是2.5D硅中介层TSV技术的关键缺点。”

虽然这限制了其在大众市场的吸引力,但对于不太敏感于成本的应用领域,如数据中心,需求仍然强劲。HBM的带宽是其他任何内存技术都无法比拟的,而使用带有微凸块和TSV的硅中介层进行2.5D集成已成为事实上的标准。

客户希望获得更好的性能,这就是为什么HBM制造商正在考虑对凸块、底部填充和模塑材料进行改进,同时实现从8层到12层再到16层DRAM模块的飞跃,这些模块能够以极快的速度处理数据。HBM3E(扩展)模块的处理速度为每秒4.8太字节(HBM3),并有望在HBM4时达到每秒1太字节。HBM4实现这一速度的一种方式是将数据线数量从HBM3的1,024条增加到2,048条。

当今,有三家公司生产HBM内存模块——美光、三星和SK海力士。尽管它们都使用TSV和微凸块来可靠地交付其DRAM堆叠和配套设备,以便集成到先进封装中,但每家公司采用的方法都略有不同。三星和美光在每个凸块层级都采用了非导电膜(NCF)和热压键合(TCB)。与此同时,SK海力士则继续采用模塑底部填充(MR-MUF)的倒装芯片批量回流工艺,该工艺可在单个步骤中用高导电性模塑材料密封堆叠。

HBM中的垂直连接是通过铜TSV和堆叠DRAM芯片之间的缩放微凸块来实现的。下部的缓冲器/逻辑芯片为每个DRAM提供数据路径。可靠性问题主要取决于回流、键合和模具背磨过程中的热机械应力。识别潜在问题需要进行高温工作寿命(HTOL)、温度和湿度偏置(THB)以及温度循环测试。还结合了预处理和无偏置湿度及应力测试(uHAST),以确定各层级之间的粘附程度。此外,还需要进行其他测试,以确保长期使用时不会出现微凸块短路、金属桥接或芯片与微凸块之间的界面分层。对于HBM4代产品,混合键合是替代微凸块的一种选择,但前提是无法达到产量目标。

用于最大数据传输量的HBM堆叠。来源:Rambus

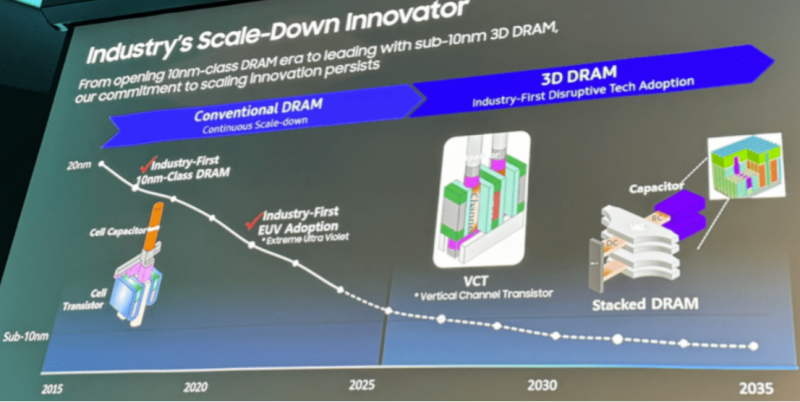

另一项正在开发的进展涉及3D DRAM器件,这些器件像3D NAND一样,将存储单元侧放。“3D DRAM堆叠将显著降低功耗和面积,同时消除来自中介层的性能障碍,”三星的金仁东表示。“将内存控制器从SoC移到基片上,将为AI功能腾出更多逻辑空间。我们坚信,定制HBM将开启性能和效率的新境界。而且,紧密集成的内存和代工能力将缩短大规模部署的上市时间,并提供最高质量。”

三星的DRAM路线图和创新。来源:Semiconductor Engineering/MemCon 2024

整体趋势是将逻辑更靠近内存,以便在内存内部或附近进行更多处理,而不是将数据移动到一个或多个处理元件。但从系统设计的角度来看,这比听起来要复杂得多。

“这是一个激动人心的时刻。人工智能如此火热,HBM就是一切。”Lam Research高级封装技术总监CheePing Lee说:“各家内存制造商都在争分夺秒,力争率先生产出下一代HBM。”

下一代是HBM4,JEDEC正忙于为这些模块制定标准。与此同时,JEDEC已将HBM3E标准的最大内存模块厚度从720毫米扩大到775毫米,这仍然允许使用40微米厚的芯粒。HBM标准规定了每引脚的传输速率、每堆叠的最大芯片数、最大封装容量(以GB为单位)和带宽。与这些标准相伴的设计和工艺简化有助于加快HBM产品上市速度——现在每两年就会推出一代新产品。即将推出的HBM4标准将定义24Gb和32Gb层,以及4-high、8-high、12-high和16-high的TSV堆叠。

HBM的演变

高带宽内存的开发可以追溯到2008年的研发工作,旨在解决与计算内存相关的功耗和占用空间增加的问题。“当时,作为最高带宽的DRAM,GDDR5的速率限制在28GB/s(7Gbps/引脚×32个I/O),”三星的Sungmock Ha及其同事表示。“另一方面,HBM Gen2将I/O数量增加到1024个,而不是降低频率至2.4Gbps,从而实现了307.2GB/s的速率。从HBM2E开始,采用了17纳米高k金属栅极技术,达到每引脚3.6Gbps和460.8GB/s的带宽。现在,HBM3新引入了每引脚6.4Gbps的传输速率,以及8到12个芯片堆叠,与前一代相比,带宽提高了约2倍。”

为了提高性能,HBM一直在向处理技术靠拢,这也为多种处理选择打开了大门。

回流焊接是最成熟且成本最低的焊接选项。“总体而言,由于安装的资本支出(CapEx)巨大且成本相对较低,因此只要可能,就会使用回流焊接,”安靠公司工程与技术营销副总裁柯蒂斯·兹文格表示,“回流焊接仍然是连接芯片和先进模块到封装基板的一种具有成本效益的方法。然而,随着性能期望的提升,以及采用异构集成(HI)模块和先进基板的解决方案空间的出现,其中一个效应是HI模块和基板出现了更多的翘曲。热压焊接和反向激光辅助键合(R-LAB)都是对传统回流焊接的工艺改进,以更好地处理在HI模块层面和封装层面出现的更高翘曲。”

微凸块金属化已被优化以提高可靠性。如果微凸块与焊盘之间的互连使用带有助焊剂和底部填充料的常规回流焊接工艺进行精细间距应用,那么底部填充空洞陷阱和残留的助焊剂残渣可能会导致凸块之间被包裹。为解决这些问题,预涂NCF可以替代助焊剂、底部填充料和键合工艺,实现一步式键合,且不会产生底部填充空洞陷阱和残留的助焊剂残渣。

三星在其12层HBM3E中使用了一种热压粘合的薄型NCF,并称其高度规格与8层堆栈相同,带宽高达1,280 GB/s,容量为36 GB。NCF本质上是环氧树脂,含有固化剂和其他添加剂。该技术有望带来更多的好处,尤其是在更高的堆栈上,因为业界正在努力减轻芯片裸片变薄带来的翘曲。三星每一代产品都会增加NCF材料的厚度。诀窍在于完全填充凸点周围的底部填充区(为凸点提供缓冲),使焊料流动,不留下空隙。

SK海力士在其HBM2E代产品上首次从NCF-TCB转换为回流焊接模制底部填充工艺。这种导电模制材料与材料供应商共同开发,可能采用了专有的注塑方法。该公司展示了使用回流焊接工艺实现的更低晶体管结温。

在HBM中,DRAM堆叠被放置在缓冲芯片上,随着公司努力在基芯片上实现更多逻辑功能以降低功耗,同时将每个DRAM核心与处理器相连,缓冲芯片的功能也在不断增强。每个芯片都被拾取并放置在载体晶圆上,焊料被回流焊接,最终堆叠被模制、背面研磨、清洗,然后切割。台积电和SK海力士宣布,未来该代工厂将为这家存储器制造商提供基芯片。

“业界对逻辑上集成存储器非常感兴趣,”新思科技研发总监苏提拉·卡比尔表示,“过去也曾研究过存储器上集成逻辑,这同样不能排除。但每种方案在功耗和散热方面都会面临挑战,这两者是相辅相成的。直接影响将是热致应力,而不仅仅是组装层面的应力。而且你很可能会使用混合键合或非常精细间距的键合,那么热问题对机械应力的影响是什么呢?”

来自底层的逻辑芯片的热量还会在逻辑芯片和DRAM芯片1之间的界面处引起热机械应力。由于HBM模块靠近处理器放置,因此逻辑芯片产生的热量不可避免地会传递到存储器上。“我们的数据显示,当主芯片温度升高2°C时,HBM侧的温度将至少升高5°C至10°C,”SK海力士高级技术经理尹秀树表示。

其他问题需要通过NCF TCB工艺来解决。在高温高压下进行的热压键合可能会引发2.5D组装问题,如凸块与下方镍焊盘之间的金属桥接或界面分层。而且,TCB是一个低吞吐量工艺。

对于任何多芯片堆叠,翘曲问题都与相对材料的膨胀系数(TCE)不匹配有关,这种不匹配会在加工和使用过程中的温度变化时产生应力。应力往往集中在痛点——即基底芯片和第一层存储芯片之间,以及微凸块层面。带有模拟功能的产品模型有助于解决这些问题,但有时这些问题的全部程度只有在实际产品中才能观察到。

结论

人工智能应用依赖于多个DRAM芯片、TSV、可能包含存储器驱动器的基底逻辑芯片以及多达100个去耦电容器的成功组装和封装。与图形处理器、CPU或其他处理器的结合是一个精心组织的组装过程,其中所有活动部件必须协同工作,以形成高效且可靠的系统。

随着行业从HBM3向HBM4过渡,制造高层数DRAM堆叠的工艺将变得更加复杂。但供应商和芯片制造商也在寻找成本更低的替代品,以进一步推动这些极快且必要的存储器芯片堆叠的采用。