本文微信公众号“岱美仪器”。

1.什么是混合键合技术

对于高级芯片封装,该行业致力于管芯对晶片和管芯对管芯的铜混合键合。这涉及将裸片堆叠在晶片上,将裸片堆叠在中介层上或将裸片堆叠在裸片上。这比晶片间接合更困难。对于管芯对晶圆的混合键合而言,处理不带颗粒添加剂的管芯的基础设施以及键合管芯的能力成为一项重大挑战。虽然可以从晶圆级复制或改写芯片级的界面设计和预处理,但是在芯片处理方面仍存在许多挑战。通常,后端处理(例如切块,管芯处理和胶片框架上的管芯传输)必须适应前端清洁级别,以允许在管芯级别上获得较高的键合良率。

2.混合键合技术的应用

用于封装的混合键合在其他方面有所不同。传统上,IC封装是在OSAT或封装厂进行的。在铜混合键合中,该过程在晶圆厂(而不是OSAT)的洁净室中进行。与处理微米级缺陷的传统封装不同,混合键合对微小的纳米级缺陷很敏感,所以,需要一个晶圆厂级的洁净室,以防止微小的缺陷破坏工艺。缺陷控制在这里至关重要。“随着先进的封装工艺越来越复杂,并且所涉及的功能越来越小,有效的工艺控制的需求也在不断增长。鉴于这些工艺使用昂贵的已知优制模具,失败的成本很高。”CyberOptics研发副总裁表示。在组件之间,有用于形成垂直电气连接的凸块。控制凸点高度和共面性对于确保堆叠组件之间的可靠连接至关重要。”

实际上,已知的良好模具(KGD)至关重要。KGD是符合指定规格的未封装零件或裸模。没有KGD,包装可能会产生低产量或失败。

KGD对于封装厂很重要。“我们收到裸模,然后将它们放入包装中,以交付具有功能的产品。人们要求我们提供很高的产量,”ASE的工程和技术营销总监在最近的一次活动中说。“因此,对于已知的优制模具,我们希望以良好的功能对其进行权面测试。我们希望它是100%。”

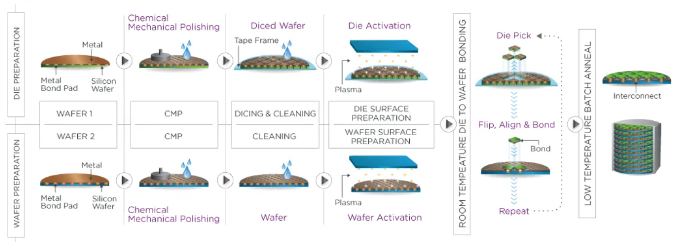

尽管如此,管芯到晶圆的混合键合流程类似于晶圆到晶圆的工艺。最大的不同是使用高速倒装芯片键合机将芯片切成小块,然后堆叠在中介层或其他管芯上。

3.混合键合过程

图1 Xperi的晶片间混合键合流程

整个过程始于fab,在那里使用各种设备在晶片上处理芯片。晶圆厂的该部分称为生产线前端(FEOL)。在混合键合中,在流动过程中要处理两个或多个晶片。然后,将晶圆运送到晶圆厂的另一部分,称为生产线后端(BEOL)。使用不同的设备,晶圆在BEOL中经历了单一的镶嵌工艺。单一大马士革工艺是一项成熟的技术。基本上,氧化物材料沉积在晶片上。在氧化物材料中对微小的通孔进行构图和蚀刻。使用沉积工艺在通孔中填充铜。这继而在晶片表面上形成铜互连或焊盘。铜焊盘相对较大,以微米为单位。此过程有点类似于当今工厂中先进的芯片生产。但是,对于高级芯片而言,最大的区别在于铜互连是在纳米级上测量的。

那仅仅是过程的开始。Xperi的新管芯对晶片的铜混合键合工艺就是在这里开始的。其他人则使用相似或略有不同的流程。Xperi芯片到晶圆工艺的第一步是使用化学机械抛光(CMP)抛光晶圆表面。CMP在系统中进行,该系统使用化学和机械力抛光表面。在此过程中,铜垫略微凹陷在晶片表面上。目标是获得一个浅而均匀的凹槽,以实现良好的良率。CMP是一个困难的过程。如果表面过度抛光,则铜焊盘凹槽会变得太大。在接合过程中某些焊盘可能无法接合。如果抛光不足,铜残留物可能会造成电气短路。

4.创新

有一个这样的解决方案。Xperi已开发出200mm和300mm CMP功能。Xperi工程副总裁表示:“在过去的十年中,CMP技术在设备设计,浆料选项和过程监控器方面进行了创新,取得了显著进步,从而实现了可重复且稳定的过程,并具有精确的控制。”然后,晶圆经过一个度量步骤,该步骤可测量并表征表面形貌。原子力显微镜(AFM)和其他工具用于表征表面。AFM使用微小的探针进行结构测量。另外,还使用晶片检查系统。这是该过程的关键部分。

图2 EVG晶圆键合机

KLA的相关人员表示:“对于混合键合,镶嵌焊盘形成后的晶片表面轮廓必须以亚纳米精度进行测量,以确保铜焊盘满足苛刻的凹凸要求。”铜混合键合的主要工艺挑战包括:控制表面缺陷以防止形成空隙;控制纳米级表面轮廓以支持牢固的混合键合焊盘接触;以及控制顶部和底部芯片上的铜焊盘的对准。随着混合键距变小,例如,晶圆对晶圆流小于2μm或管芯对晶圆流小于10μm,这些表面缺陷,表面轮廓和键合焊盘对准挑战变得更加重要。”这可能还不够。在此流程的某个时刻,有些人可能会考虑进行探测。

FormFactor高级副总裁表示:“传统上认为直接在铜垫或铜凸块上进行探测是不可能的。“主要关注的问题是如何在探针间端和凸块之间保持稳定的电接触。”为此,FormFactor开发了一种基于MEMS的探针设计,称为Skate。结合较低的接触力,间端会轻柔地穿过氧化层,从而与凸块形成电接触。EVG的晶圆键合机是适用于封装行业中的这种芯片封装混合键合技术应用的。