本文来自微信公众号“半导体封测”。

半导体产业一直致力于追求更先进的工艺制程,从7nm到5nm,再到3nm,不断突破技术极限。2022年,台积电宣布成功大量量产3nm鳍式场效电晶体制程技术,这标志着我们在半导体技术领域又迈出了重要一步。然而,随着1nm工艺的逼近,业界也面临着前所未有的技术挑战。

从3nm跨越到1nm,需要克服许多技术难题。首先,随着芯片制程的缩小,量子效应和热效应会变得越来越严重,这给芯片的设计和制造带来了极大的挑战。其次,随着工艺制程的缩小,材料的性能和制造过程中的缺陷都可能成为影响芯片性能的关键因素。因此,为了实现1nm工艺的量产,我们需要探索新的材料和制造工艺,以确保芯片的性能和可靠性。

尽管面临这些技术挑战,但业界对于1nm工艺的追求并未放弃。1nm工艺的应用将带来更高的性能和更顶尖的技术,这无疑会为半导体产业带来巨大的变革。因此,无论是从技术还是商业角度来看,1nm都充满了无限的诱惑。

01

1nm,念念不忘

工艺制程的研发和生产需要大量的资源,包括技术积累、资金、人才和设备。从5nm走到3nm,生产成本也翻了一番,因此并非每个机构和企业都有能力追求1nm。

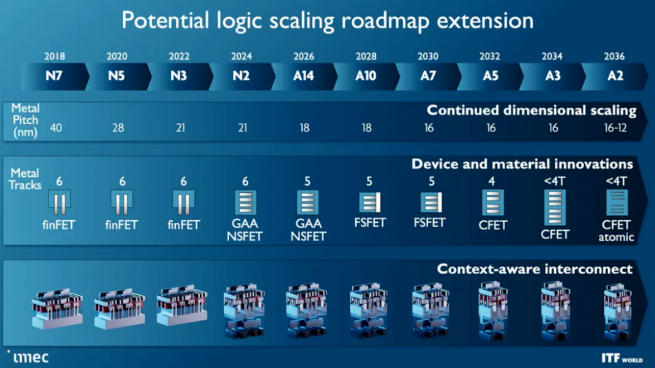

目前,日本计划与法国合作开发1nm制程半导体,具体合作方式是日本芯片制造商Rapidus与东京大学、法国半导体研究机构Leti进行人员交流和基础研究共享。IBM也在积极研发1nm芯片技术,已经推出了全球首款2nm芯片,并展示了其为通向1nm及以上准备的技术。Imec也在研究1nm以下晶体管的路线图,并与ASML签署了合作协议。台积电则是目前唯一一家能够成功实现3nm量产的晶圆厂,也在研究1nm技术。

虽然追求1nm需要面临诸多技术挑战和成本压力,但这些机构和企业仍然不断探索和创新,以期在未来的竞争中占据优势。

来源:IMEC

芯片龙头英特尔对于1nm的诱惑同样无法抗拒。从工艺节点来看,英特尔目前准备将Intel 4,用于Meteor Lake处理器和Granite Rapids,下一步将是Intel 3,它将使用EUV光刻来实现更大的模块化,PPW增加到18%。而英特尔最新的工艺是20A和18A。Intel 20A本来被称为Intel 1,但是由于英特尔想要“更好的唤起下一个创新时代”,将其命名为20A。

现在问题来了:1nm未来,如何实现?

02

2D材料

为了实现1纳米工艺几何结构的工作,寻找合适的晶体管结构和材料仍然是一个重要的研究方向。使用非硅材料有利于制造非常微小的晶体管,因为它们可以在纳米尺度上保持稳定性和性能。

在2019年,IMEC在IEEE会议上展示了使用二维材料可以实现1纳米以下的工艺节点。他们展示了使用二硫化钼(MoS2)作为材料,制造出了具有微小特征尺寸的MOSFET,这为晶体管的极端缩放开辟了新的途径。MoS2是一种二维材料,这意味着它可以以稳定的形式生长,厚度仅为一个原子。最重要的是,在这个尺度上,MoS2具有原子精度。

麻省理工学院、南洋理工大学和台积电的研究人员发现,二维材料与半金属铋(Bi)结合可实现极低的电阻,克服了实现1纳米芯片的挑战。

台积电在2D材料方面也取得了突破,逼近1nm工艺节点。他们与麻省理工学院和南洋理工大学合作发表了一篇论文,描述了金属引起的导电间隙对制造挑战的影响,以及单层技术如何受到这些金属引起的间隙的影响。

在论文中,他们建议使用后过渡金属铋和一些半导体单层过渡金属二硫族化物来减小间隙的尺寸,从而生产出比以前小得多的2D晶体管。台积电在实验中尝试了各种低电阻的半导体材料,包括二硫化钼(MoS2)、二硫化钨(WS2)和二硒化钨(WSe2)。

03

改变铜(Cu)互连

在计算机芯片中,半导体组件之间的连接线路被称为互连。简单来说,互连是电流在芯片中的晶体管、存储器、处理单元和其他组件之间的流动方式。如果互连的传输效率越高,那么芯片的效率也会越高。在1997年之前,人们通常使用铝互连,但是IBM发现了更有效的铜互连。由于铜线的导电电阻比铝线低约40%,这意味着处理速度可以提高约15%,因此铜互连逐渐成为了行业标准。

然而,随着技术的发展,铜互连也遇到了瓶颈。铜互连需要阻挡衬里材料来形成适当的布线结构,但是随着器件尺寸的缩小,可用于铜布线和衬垫材料的空间变得更小。因此,业界一直在寻找其他金属可以替代铜互连。

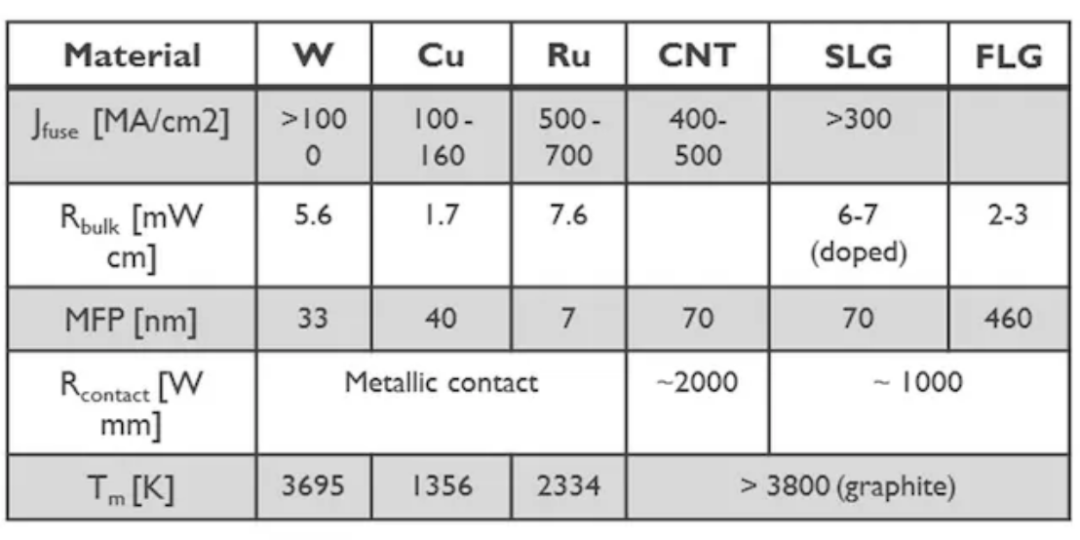

碳纳米管(CNT)、单层石墨烯(SLG)和少层石墨烯(FLG))与其他相关互连材料(钨(W)、铜(Cu)和钌(Ru))的性能比较来源:IMEC

IBM:使用钌

IBM正在寻找使用钌来解决铜互连遇到的瓶颈问题。钌可以扩展到1纳米及以上节点,并且仍然是一种有效的导体,因此不需要衬垫,这有助于节省空间。

通过减色图案化方法形成的钌也有可能用于一种新型互连集成方案,称为顶通孔集成。在这种情况下,互连通孔形成在导线的顶部,而不是导线的下方,从而允许为最关键的互连层形成连续的导线和自对准通孔。此外,通过这种顶通孔集成牢固地形成嵌入式气隙,从而减少互连寄生电容,也将有助于实现更快、更低功耗的芯片。

IBM的研究人员使用极紫外光刻(EUV)双图案现有的机器上创建测试结构,结果表明能够实现突破。这些研究结果表明,使用钌作为替代材料可以克服铜互连的限制,并为更小、更快和更高效的芯片提供新的可能性。

IMEC、台积电:使用石墨烯

与IBM不同,台积电尝试使用石墨烯进行多层布线。人们对石墨烯互连应用的兴趣并不令人意外,因为石墨烯表现出高本征载流子迁移率和大载流能力,同时具有高导热性和抗电迁移的竞争稳健性。此外,石墨烯可以制成原子级厚度,有助于减轻厚度对RC延迟的影响。

台积电表示,当制作不同宽度的互连原型并将其电阻与铜互连进行比较时,发现宽度为15nm或更小的石墨烯互连的电阻率低于铜互连的电阻率,石墨烯的接触电阻率也比铜低四个数量级。将金属离子嵌入石墨烯中可以改善互连的电性能,使其成为下一代互连的有前途的材料。

IMEC认为石墨烯和金属的混合结构非常有希望成为1nm的候选者,同时也在考虑钌(Ru)作为铜互连的替代品。这些研究表明,石墨烯和钌等新材料在芯片制造领域具有广阔的应用前景,可以为更小、更快和更高效的芯片提供新的可能性。

04

改变器件架构

如上文提到,IBM对于1nm的努力除了选择钌互连外,还有一个就是VTFET架构。IBM认为,使用VTFET,晶体管组件垂直堆叠在一起,而不是横向堆叠,这是自计算机时代诞生以来设计芯片的标准。这极大地增加了单个芯片上可以安装的晶体管数量,就像摩天大楼城市的人口密度远高于联排别墅郊区的人口密度一样。IBM的研究表明,VTFET设计的规模可以远远超出IBM Research于2021年首次推出的最先进的2纳米节点纳米片设计的性能。

IMEC认为能够超越2nm的器件架构是Forksheet架构。这种新的forksheet器件架构是GAA纳米片器件的自然演变,允许轨道高度从5T扩展到4.3T,同时仍然提供性能增益。或者,通过叉板设计,可用空间可用于增加板宽度,从而进一步增强驱动电流。这些研究表明,新的芯片设计架构和材料为更小、更快和更高效的芯片提供了新的可能性。

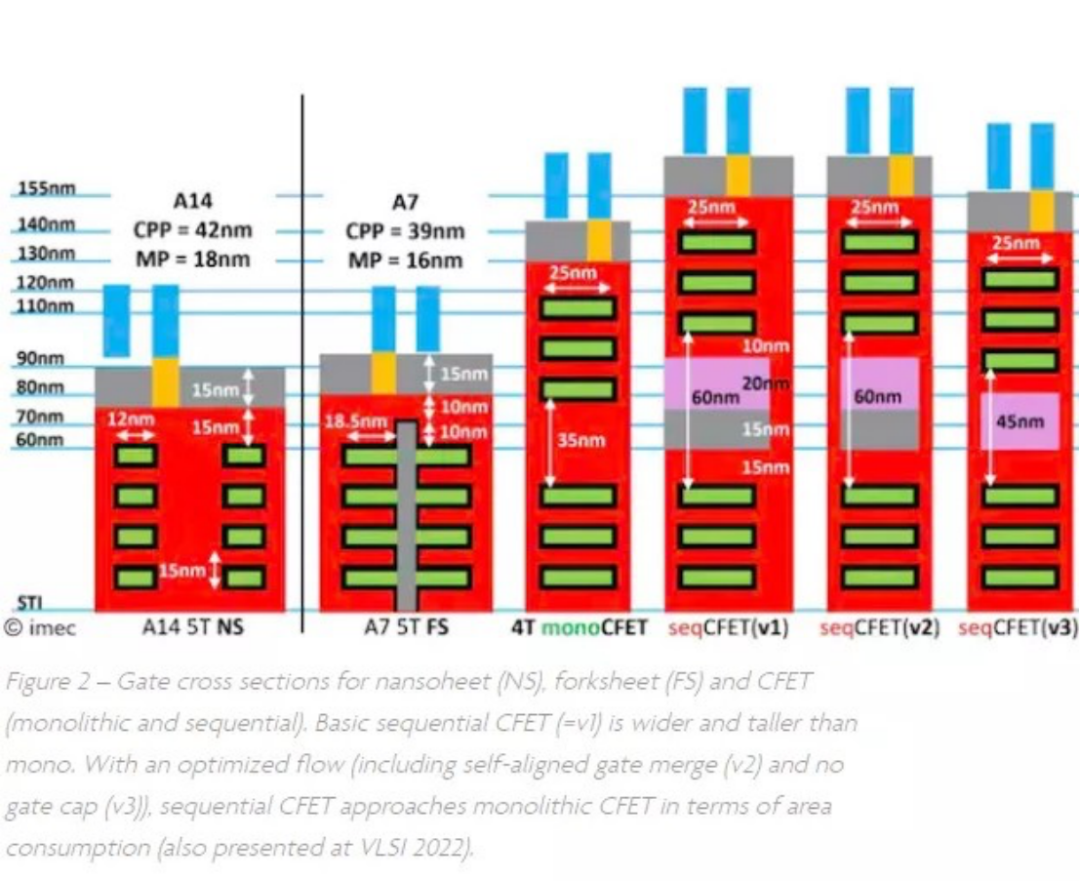

图侧四个结构,均为CFET的变种来源:imec

英特尔则是认为可以使用一种GAA FET的最新形态——堆叠式CFET场效应管架构。这种架构的集成密度进一步提升,将n型和p型MOS元件堆叠在一起,可以堆叠8个纳米片,比RibbonFET多一倍。目前,英特尔正在研究两种类型的CFET:单片式(monolithic)和顺序式(sequential)。不过,英特尔的CFET架构并不是独立提出的,而是与IMEC机构长期合作的结果。

05

总结

在科技领域,1纳米无疑具有巨大的吸引力。然而,1纳米技术也带来了许多挑战。对于许多公司和科研机构来说,1纳米可能是技术上的一个重要目标,它不仅仅代表着物理极限,更是一个巨大的商业机会。例如,1纳米晶体管可以带来更快的处理器、更小的内存单元和更高效的能源储存等。

然而,从目前的技术发展来看,从3纳米到1纳米,摩尔定律的延续面临着巨大的挑战。产业界普遍认为,学术界取得的突破性进展并不一定能很快应用于商业化的芯片生产。例如,3纳米芯片的良率似乎仍是一个问题。因此,要克服1纳米技术所面临的巨大挑战,需要更多的深入研究和探索。