本文来自中国电子报、电子信息产业网,作者/沈丛。

编者按:摩尔定律是由英特尔创始人之一戈登·摩尔提出的,其核心内容为:集成电路上可以容纳的晶体管数目大约每18个月便会增加一倍。几十年来,英特尔也一直是摩尔定律最坚定的捍卫者,紧紧追随着摩尔定律的发展。但随着芯片内晶体管密度越来越高,摩尔定律的延续变得愈发困难,这也成为了业内面临的共性问题。近日,中国电子报总编辑胡春民采访了英特尔研究院副总裁、英特尔中国研究院院长宋继强,就此问题展开了深入讨论。

对话人:

英特尔研究院副总裁、英特尔中国研究院院长宋继强

《中国电子报》总编辑胡春民

时间:2022年6月10日

地点:赛迪大厦

摩尔定律仍能以一定节奏延续

胡春民:有人说当前摩尔定律已经到达了极限。若想延续摩尔定律,需要更具颠覆性的技术创新和突破,英特尔对延续摩尔定律有什么建议?

宋继强:摩尔定律不仅仅是物理定律,也是对于半导体未来技术以及经济发展的预测。在表述上,是指在一定尺寸内的半导体晶体管密度,以各种各样的方式实现提升。同时,它还有另一个特点,即半导体的性能达到平均水平后,半导体的价格也会以一个指数级的方式下降。因此,从整体上看,摩尔定律其实是通过预测半导体指数级提升的方式,来推动半导体产品的性价比。

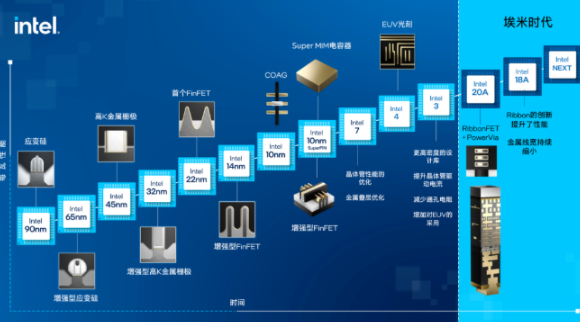

摩尔定律发展历程(图片来源:英特尔公司)

由此可以看出,摩尔定律并不是一个技术定律或者物理守则,而是半导体领域专家对产业发展方向的大胆预测,并且把它视为一种信念。当然,光有信念不够,还要去执行、去推动它的发展,需要通过实际的技术进步和生产工艺的提升来推动摩尔定律相关技术的落地。

几十年来,英特尔既是摩尔定律的提出者,也是守护者和推动者。在过去的二十年中,摩尔定律已经多次被传停滞,甚至是要终结。但事实上,每次有这样的困难时,都意味着半导体技术的发展遇到了巨大的技术挑战,导致短期内没有合适的半导体技术来推动摩尔定律按原本的节奏发展。但每当大家认为摩尔定律要失效时,也总会出现一些新的技术,并应用到产业的发展中,推动摩尔定律继续前行。例如,2008年高K(介电常数)电介质的金属栅极技术的出现,突破了芯片在32nm工艺制程的卡点。此外,3D FinFET架构的出现,帮助芯片制程成功突破28nm工艺制程。

英特尔晶体管的创新里程碑(图片来源:英特尔公司)

但是,随着芯片制程进入到5nm、3nm,很多工艺结构的设计已经开始接近于原子层面,对设计的精度、良率都有很高的要求,也使得技术的突破变得更加困难。因此,如今的芯片微缩,将更加依赖光刻机技术以及新的架构设计方法。

首先,在光刻技术方面,需要大大提升光刻机的精度,使其能光刻更细微尺寸的芯片。其次,在芯片尺寸缩小的同时,若想有效提升芯片性能,需要新的架构设计方法。如今,业内认为全新的GAA(Gate All Around)的架构设计方式,能够有效提升先进制程芯片的性能。英特尔以GAA为根基,设计出RibbonFET架构。在英特尔芯片制程进入埃米后(例如Intel 20A制程工艺),将会采用RibbonFET架构。

对于半导体行业而言,摩尔定律如同一面旗帜,若遵守它,就能够用各种创新来达到相应的技术水平。此外,摩尔定律的发展也并非凭一己之力便可达成,需要产业链上下游一起合力推动。如果大家都相信摩尔定律能够发展下去,那么它仍然能够以一定的节奏延续。

制程工艺的先进性要综合评判

胡春民:摩尔定律的延续通常基于制程工艺的推进。业内已经有代工企业实现了5nm、4nm的量产并走向更微小的制程。英特尔在制程工艺上和其他厂商有哪些不同?为什么要坚持这种路线?

宋继强:从90年代后期起,不同厂商对制程工艺节点的命名方式已不再统一。此前,由于人们可以比较精确地测量出晶体管栅极的长度,企业往往会用晶体管栅极的长度作为某一代芯片制程的名称。但是,在芯片微缩的进展放缓后,晶体管栅极长度的缩小不如从前明显,但人们依旧希望在芯片制程的命名上体现摩尔定律的延续。因此,在进入21世纪后,各个厂商的命名规则便出现了不一致的情况,有的厂商依旧采用栅极长度命名,有的则采用其它的特征尺寸来命名,从而强调其可以将制程做得更小的能力。

因此,芯片制程的数值大小,对于如今的半导体制程工艺而言,已经没有太大的参考意义。在衡量芯片性能方面,其他数值同样具有参考意义,例如芯片中晶体管的情况也是衡量芯片性能的重要指标,即晶体管能达到怎样的密度等。这些技术水平甚至比纳米数值更具有说服力。

可见,若想衡量半导体制程工艺的先进性,需要结合许多方面的指标来综合评判,而不是仅仅通过几纳米的数值一概而论。对于英特尔而言,在推进工艺制程方面一直坚持严格要求、稳步前进,不一味追求速度。例如,英特尔的14nm、14nm+、14nm++、10nm、10nm+等制程工艺,实际上每个加号都代表了一次工艺上的提升,有的是10%的提升,有的是20%的提升。有时候友商会把这种提升直接当成一个新的制程节点发布,但英特尔没有。

英特尔最新制程工艺路线图(图片来源:英特尔公司)

英特尔在14nm到10nm的推进过程中遇到了一些困难,相比友商慢了一些。目前英特尔在最先进的制程工艺节点上,大概比友商慢了一年到一年半左右。所以,英特尔提出了IDM 2.0的新战略,目标是在4年内推进5个制程工艺节点。在这个战略下,当英特尔推进到Intel 20A时,制程工艺大概能够与业内顶尖水平齐平,甚至能稍微强一些。到Intel 18A时,英特尔在制程工艺上能够回到业内领先地位。而这并非空穴来风,是以各种精确的指标进行衡量后得出的。

胡春民:Intel 18A和Intel 20A在数字上的差别看上去很小,两者在技术上会有怎样的优化和进步?

宋继强:二者之间的差距,主要体现在RibbonFET架构性能上的提升,这一架构将会在Intel 20A出现时正式现身,到Intel 18A时会变得更加完善,从而进一步优化芯片性能,在供电方式、开关速度控制、功耗等方面均会进行优化,并在此后的工艺上持续提升。

先进工艺芯片的开发流程,涉及上千个步骤,还需要以非常高的良率去量产芯片,实属不易。架构设计很难一步到位,需要不断地优化升级。晶体管可以视为一块块乐高,每一小块均可以打造不同的架构产品。有些架构可以打造高性能计算,有些架构在注重性能的同时,也能实现更低功耗。同时,不同的性能需求对晶体管测试的场景也有不同的要求。在搭建的过程中,需要不断对架构进行测试,从而推动架构的持续优化,实现技术的持续进步。

新架构是延续摩尔定律的重要方式

胡春民:如今,部分代工厂商转向了GAA架构以推动更先进制程的研发。英特尔在架构创新突破上和其他企业有哪些不同?

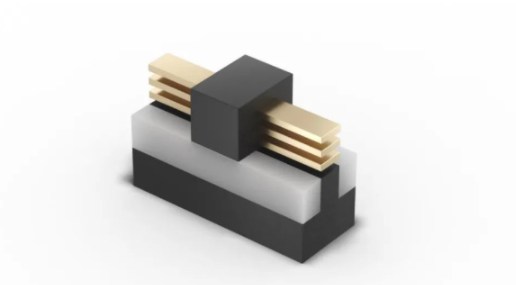

宋继强:GAA是一种晶体管搭建的结构方式,是用栅极包住两边的沟槽鳍片的结构。这是一种通用的架构,但各家对于具体的晶体管结构设计是各有所异的。

英特尔全新RibbonFET晶体管(图片来源:英特尔公司)

英特尔在GAA晶体管上实现了创新架构RibbonFET,RibbonFET架构可以让一个栅极同时包住多个用于电流导通的构槽。同时,沟槽鳍的设计可以根据不同需求,去拉宽或者收窄,从而在整个设计上变得相对灵活,多片的鳍可以被一个栅极完全包住,在拉高尺寸的同时不占用过多的平面尺寸。鳍在加宽的同时,也能保证电流的通过量足够大,且不会增加整体结构的尺寸,这也是英特尔在架构设计上的独特之处。

如今整个行业都很看好GAA机构,纷纷开始将其用在晶体管的结构设计中,但能否实现芯片的量产最为关键,如今看来也很有难度。

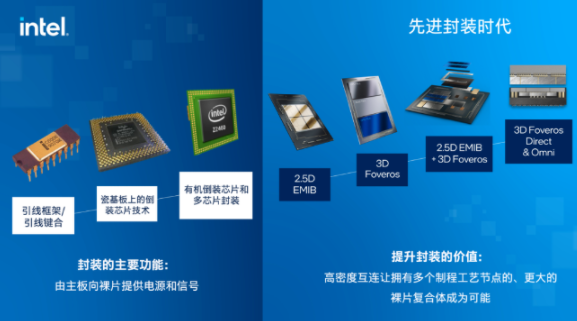

先进封装将推动摩尔定律延续

胡春民:封装曾被视为集成电路领域技术含量相对比较低的环节,如今业内提出了先进封装概念,包括3D堆叠等技术,并将其视为推进摩尔定律发展的关键。先进封装技术如何推进摩尔定律的发展?英特尔在这方面有哪些突破?

宋继强:先进封装将会成为延续摩尔定律的一个重要技术方向。此前,人们通常把目光焦距在芯片里的晶体管设计,致力于如何把单独的die(独立的功能芯片)做好,包括如何优化结构、改善供电等。在封装方面,传统的封装在die之外的带宽、功耗以及连线的间距差别很大,导致在同一个芯片系统里的die之间无法集成,也难以提升芯片的性能。

英特尔封装技术的创新里程碑(图片来源:英特尔公司)

因此,仅通过传统封装的方式,很难有效提升芯片性能,但这一系列问题在先进封装中得到了有效解决。例如,采用先进的混合键合技术,能够把在封装中的间距尺寸降到10微米以下。因此,采用先进封装技术,芯片中的特征尺寸差别能够缩小很多,相互间连接的电阻、连线长度的功耗也会随之下降,可以达到联合优化的效果,从而有效提升芯片性能。

在先进封装中,除平面封装外,还可采用3D封装的方法提升芯片性能。3D封装把计算单元和计算单元封在一起,使芯片密度大幅提升。

3D封装技术的出现,意味着在芯片的平面方向将不再占用更多尺寸空间,而是通过竖直堆叠的方式向上延伸,虽然效果会更好,但技术难度也会随之提高。首先,连线之间传输的信号速度会变快;其次,运算器的功耗也会变大。因此,在3D封装领域中,功能密度的提升、功耗的降低等,是未来需要优化的方向。

Foveros是英特尔推出的3D封装技术,包括已经推出的Foveros omni和Foveros direct技术。这些技术均是在竖直方向上,对计算单元进行有效连接,能够顺畅地供电,也不需要在芯片以及die上打孔,从而节省宝贵的平面资源。

胡春民:在先进封装方面,大企业针对异构集成、芯粒等技术,开展了哪些合作?

宋继强:先进封装在2D集成时,各个芯片或芯粒之间可以用主流的方式来进行互联,但在2.5D以及3D的异构集成中,用主流的方式连接会变得相对困难,需要统一的互联标准。因此,英特尔发起了UCIe(通用芯粒互连技术)联盟,意在制定统一、公共的互联标准。UCIe联盟包含了芯片设计厂商、封测厂商等半导体产业链中各个环节的厂商,使得各产业链之间形成互联互通的关系,有利于标准的制定。

UCIe联盟的成立,不仅使英特尔能够与其他厂商共享技术和接口,还能够有效推动产业链上下游伙伴,一起形成更优的产业互联技术,推动产业发展。

胡春民:在异构集成技术领域,中国企业如何更好地参与?

宋继强:如今中国企业都在积极参与异构集成技术的发展。UCIe联盟已经有几家中国的企业。异构集成也是中国半导体产业着重研究的技术领域之一,产学研各个方面都十分重视。例如,中国科学院院士刘明去年就提到了混合键合技术;清华大学教授、国际欧亚科学院院士魏少军也在今年3月份的一个大会上特别提到了异构集成,并表示以三维混合键合技术为代表的微纳系统集成,将是未来半导体延续摩尔定律的主要手段。由于传统封装领域和先进封装领域之间还有很大的技术鸿沟,中国若想更好地发展异构集成技术,需要结合学界和业界两方面的能力来共同推动发展。

异构计算使芯片设计更加灵活

胡春民:异构计算对摩尔定律延续能起到怎样的作用?

宋继强:如今人们更加关注异构计算技术,是由于异构计算能够在已有的芯片制程基础上,不通过缩小芯片制程的方式,只通过计算架构的设计创新优化芯片性能。在未来的芯片设计中,将既有传统的标量计算架构,也会有矢量架构,甚至还会有矩阵运算等架构。将这些架构整合后,能更有效地利用底层芯片资源,发挥更高效的计算能力,从而有效提升芯片性能。

英特尔全新x86内核架构:能效核、性能核(图片来源:英特尔公司)

随着数字化转型的加速,各行各业对算力的需求越来越旺,只用常规的芯片架构来处理这些数据是远远不够的。采用多种架构组合的方式,能够根据不同的功能来匹配适合的架构进行数据处理,使工作变得更加高效。英特尔CPU就采用了异构计算技术,芯片内既含有能效核E-core(Efficient Core),也含有性能核P-core(Performance Core),兼顾了芯片中的能效和性能,在提升芯片性能的同时,还能根据客户需求进行灵活的调整。

宽禁带半导体暂时无法替代硅基半导体

胡春民:近期宽禁带半导体技术被热炒,一些碳基功率器件开始在汽车上应用。碳基半导体未来是对硅基半导体的替代吗?

宋继强:相比较于传统的硅基半导体而言,宽禁带半导体在一些功率器件中的应用较有优势,但并不意味着它能替代硅基半导体,因为宽禁带半导体的应用领域还十分有限,远不及硅基半导体。例如,宽禁带半导体并不适合用来做计算部件,无法在CPU领域应用。宽禁带半导体是另一种技术方向,并不是硅材料的替代技术。

四大超级技术力量推动数字化进程

胡春民:英特尔CEO帕特·基辛格说过,当今时代的四大超级技术力量是无处不在的计算、从云到边缘的基础设施、无处不在的连接和人工智能。这四大技术对未来万物互联以及数字化发展都有很大的帮助。对此英特尔都有哪些布局?

宋继强:这四大技术力量被英特尔视为数字化转型的四个超级力量,也是英特尔重点布局的技术领域。无处不在的计算,意味着未来的万物互联技术将变得更加智能,使未来的计算不再仅限于手机、电脑等设备的连接,而是能将更多设备进行连接。这也意味着未来的常见设备,无论是植入式还是连接式,均需要加上计算能力。例如,会议室的桌子也能具备触摸、交互、录音等能力;墙壁甚至可以自动变成投影或者可交互的场景。

无处不在的计算力量可能只存在一个独立的设备中,也可能存在于多个连接的设备中,但对于通信技术水平的需求非常高。在通信的过程中,设备需要从其他设备中获取数据,或者获得一些额外的计算资源。因此对于通信设备而言,需要全方位的连接,既需要有前端、后端一站式的连接——比如通过5G、Wi-Fi提供低延时、高通量的连接,也需要一些有线的连接,比如运营商的接入网与骨干网之间的连接等。

可见,无处不在的计算力量也需要无处不在的连接。为实现无处不在的连接,英特尔致力于通信技术创新,包括4G、5G甚至6G的网络标准化定制技术。在运营商、服务商的体系中,英特尔有FlexRan软件技术作为支持。在硬件技术中,英特尔能够提供智能网卡、IPU等网络加速技术的支持。

在从云到边缘的基础设施中,除了强大的硬件支持,还需要具备高度互通性的软件,使硬件发挥出效力,并做好对硬件资源的协调和调度。因此,英特尔在软件层面提供了不同种类的开发包,提供功能更加完善的软件堆栈。

在从云到边缘的基础设施中,异构计算是关键技术。但异构计算单元的调度成为了新的挑战,如何实现在异构计算单元调度完整的同时,达到降本增效的效果,需要产业界的协同探索。因此,英特尔与合作伙伴开启oneAPI计划,为异构计算提供统一的编程框架,覆盖从云到端的边缘计算,使开发者们能够灵活调度计算资源。

如今的数据量呈指数上升,单凭人力难以处理。因此,人工智能技术成为了四大超级力量之一。在未来的数据中,除了数字化系统本身产生的数据外,还会有物理世界折射到数字化领域的数据,包括但不限于人类日常的视觉、语音等数据。这些海量数据都需要AI算法来进行处理,并将其进行优化后与硬件连接。对数据进行有效整合,并保持垂直性,才能使人工智能真正发挥高效率优势并提高生产力。

未来芯片的性能迭代与成本预期仍有据可依

胡春民:此前,在摩尔定律的发展过程中,总会出现一些具有特征性的规律,使得人们能按照此规律准确地预测出下一代芯片的成本、性能等各项指标。在后摩尔时代,芯片的性能迭代与成本预期,是否仍然延续同样的规律?

宋继强:规律会依旧存在,但不会是长期稳定的规律。这是由于此前的技术难点不高,在芯片迭代的过程中,规律性也相对稳定,人们也能够提前很久预测出芯片技术的发展情况。但随着技术难度越来越大,不定性因素增多,人们很难提前很久就预测下一代芯片技术的相关情况,往往在技术临近推出时,才能得到确切信息。

例如,英特尔的Intel 18A芯片,现在还无法确切地知晓相关技术细节,需要等2023年Intel 20A即将发布之时,芯片制程正式进入到埃米之后,才能得知具体情况。Intel 18A芯片的研发,需要有2000多道工艺流程,在这个过程中会出现哪些变数,目前还难以定论。因此,如今的规律性虽然不如以前强,但是依旧存在。