当今社会,网络作为信息与价值传递的中枢,其安全性关系到信息安全、经济安全和国防安全。加密是网络安全体系的重要一环,成熟的密码体系,是网络安全的基石。近年来,随着密码相关的法律法规不断落地,政策的导向日益清晰,合规性的需求推动着安全应用的广泛落地,进而对加密软硬件的需求越来越大,要求也越来越高。另一方面随着网络带宽的升级,5G通信和物联网应用的流行,高速密码应用场景逐渐泛化。高速密码处理器作为安全应用中,最底层的核心器件,日益受到关注。

关键词:高速密码处理器;安全芯片;密码算法;数据安全

引言

现代社会,电子网络是信息流动的中心枢纽。其在日常生活、金融、制造业等领域,得到广泛的应用。随着网络的普及,基础带宽的越升,许多新兴的应用场景随之出现,如大规模电子支付,数字货币,物联网IoT,车联网等。

在这些新兴场景中,电子网络不再仅是用来传递信息,更多是传递信用和价值,促进更大规模的,更深刻的社会分工和协作,即从信息网向价值网拓展。能否保证数据的机密、不可篡改、不可抵赖,通信的保密、完整是电子网络能否发展成为价值网络的关键。其中加密技术是整个网络应用和实现的基石。在大规模实际的应用中,成本、效率、能耗和时效性成为了当前加密技术的瓶颈,因此高速密码专用处理器日益受到关注和重视。

01

高速密码处理器的典型架构

当前高速密码处理器主要有如下几种实现方式,其基本原理,设计考量如下。

通用处理器以指令驱动方式执行,数据通路采用冯洛伊曼架构。通用处理器作为密码算法的一种实现方案,完全可以满足高灵活性的要求。通用处理器可以通过指令编程快速支持不同的密码算法。但由于通用处理器是使用一套通用指令集,其计算架构没有针对密码算法的特点进行优化,密码算法中的S盒、置换等核心计算模块在通用处理器上运行较慢,导致算法整体性能较低。同时,对高灵活性的追求使得通用处理器的控制逻辑占据了相当大的比重,其计算资源局限了密码算法的实现,这也是其密码性能低下的原因之一。为了获得更强的密码算力,通用处理器需要提高运行频率和指令并行性,但其控制逻辑的功耗和面积会增加得更快,这使得其很难提高密码算法的能效和面积效率。

专用集成电路是根据不同算法定制的具有特殊规格的集成电路。通过优化特定密码算法的数据路径和流水线,该方案可以实现高性能、小面积和高能效。然而,这种实现灵活性差,单个芯片支持的算法数量有限。在市场上,以这种方式实现的芯片大多出现在特殊加密领域。

专用指令集处理器的体系结构是根据特定应用领域的算法特点进行指令集优化的处理器。这使得其比通用处理器在该领域更高效。密码算法的设计通常基于一定的数学理论,涉及一定长度密钥的大量迭代运算,在实际应用中往往需要处理大量信息,因此密码算法计算强度高,属于计算密集型应用。根据密码算法的特点,专用指令集处理器可以加强数据路径中的计算资源,简化体系结构设计中复杂的控制逻辑,使专用指令集处理器的计算特性更好地匹配密码算法的特性。使用专用指令集处理器作为密码算法的实现方案,可以满足支持不同密码算法的灵活性要求,获得比通用处理器更高的能效和面积效率。

可重构构架是一种硬件资源功能和互联结构可以根据计算任务的不同而改变的计算架构。在执行具体的计算任务前,先对计算资源进行配置。配置完成后,其执行过程与专用集成电路类似,是由数据驱动,以获得较高的执行效率。可重构构架有效的结合了通用处理器和专用集成电路的优势,同时具有专用集成电路的高能效和通用处理器的高灵活,比较好的满足复杂的安全应用对灵活性的需求。

美国加州大学的杰拉尔德埃斯特林最早提出可重构的计算体系设想,但是受限于当时的制造水平,无法实现出可重构构架所需要的硬件资源。20世纪90年代,随着集成电路制造能力的突飞猛进,可重构理念重获学术界的青睐,并引起工业界的关注。之后,加州大学伯克利分校的可重构技术研究中心的两位教授,对可重构技术提出了一个新的定义:可重构构架是一种计算机构架,与其他构架相比,其有两个特点。其一是硅后定制能力,即芯片制造完成以后,可以根据计算任务的需要,而改变计算的功能,这种改变与专用集成电路不同。另一点是相较于只能按照指令顺序执行的传统通用处理器,可重构硬件可以根据算法的特点,对计算引擎进行空间映射。

按照计算的颗粒度,可重构构架可以分为粗颗粒可重构和细颗粒可重构。计算的颗粒度主要指计算中,数据路径的位宽。现场可编程逻辑器件是最典型的细粒度可重构计算架构,广泛应用于密码算法的实现。常见的分组密码,流密码和哈希算法都在现场可编程逻辑器件上实现了非常高的性能。

但由于现场可编程逻辑器件本身的结构特点,实际的应用中有一定的局限性。现场可编程逻辑器件的基本运算单元包括触发器、LUT查找表和数字逻辑门。密码算法通常位宽比较大,在现场可编程逻辑器件中,算法也只能以单比特的颗粒度配置和运行,硬件资源与计算的颗粒度无法很好的匹配。另一方面,现场可编程逻辑器件的布线资源复杂,配置信息的数量巨大,配置过程的时间也比较长。

这些因素导致现场可编程逻辑器件,如果需要高性能地实现多种密码算法,特别是公钥算法,逻辑资源消耗巨大,成本比较难以控制。可重构的另一种选择是粗粒度可重构架构。密码领域,颗粒度可选用8位、16位或32位作为计算的基本单元。同时使用更大粒度的计算单元,如加乘法器、移位器等,用来取代了现场可编程逻辑器件中位运算的查表等运算单元,以简化互连结构。

这使得粗粒度可重构架构比现场可编程逻辑器件更具有灵活性,适合于密码算法的实现。密码算法在粗粒度可重构架构实现时,可以充分利用算法的计算特性,优化粗粒度的计算资源,并设计相应的配置组织和调度机制,提高密码算法的能效和区域效率。

02

高速密码处理器设计的挑战

高速密码处理器应用在服务器端和中心端网络设备,需要灵活支持多种密码算法和常见安全协议,同时对性能有不低的要求。另一方面,随着密码服务的云化趋势,高速密码处理器更加需要支持云场景的特性。具体可从以下几个方面体现。

(1)网络应用场景中,使用多种安全协议保证通信安全,因此需要高速密码处理器尽可能灵活地支持所有主流算法。主流的密码算法分为公钥算法、对称算法和哈希算法三类。公钥算法的主要运算单元是大数模幂运算;哈希和对称算法的主要运算单元是逻辑、算术、移位、和置换。同时密码算法按照特征可以分为对称密码和非对称密码。对称密码是指加解密过程使用相同的秘钥。常见的分组密码,流密码都属于对称密码。非对称密码是指加解密的过程中,使用两把不同的秘钥。两把密钥分别称为公钥和私钥。公钥可以公开,私钥保密。如果使用公钥加密,可以用私钥进行解密,反之亦然。

在常见的安全协议中,多种加密算法相互结合使用。大部分情况,通信的两端通过协商,决定具体采用何种密码算法,因此位于服务器端的安全处理器需要具有足够的灵活性。网络安全系统,采用的不同的安全协议,保障不同的网络传输层次的通信安全。常见的安全协议包括应用层的SSH、OpenPGP和S/MIME,网络层的IPSec,传输层的TLS/SSL等。这些协议中需要不同的密码算法。例如,在IPsec协议中,为了完成信息加密和数据完整性验证的安全策略,需要支持AES、DES、3DES等分组密码算法和SHA256、MD5等哈希密码算法。

同时,由于现代安全协议独立于密码算法,协议中使用的密码算法是基于会话协商的。如图1所示,HostA和HostB需要协商会话中使用的加密算法类型和密钥,才能通过IPsec协议完成数据加密传输。而且安全协议和密码算法本身也在发展,旧的协议标准即将到期,安全协议中需要支持的密码算法数量也在不断增加;现有的密码算法可能会因为被攻破而被安全性更高的新算法取代。因此,密码算法的实现需要算法升级的能力,以满足同时期存在的多个安全协议,满足一段时间内安全协议和密码算法的升级。

图1 IPSec典型流程

完整的加密过程主要分为两步,协商秘钥和数据流加密。期间需要多种密码算法的参与。

(2)在特殊领域的应用中,通常通过不规则地改变密钥和算法来加强系统的安全性,使得密码算法的实现满足高灵活性的要求。除了公开密码算法之外,各国还开发了非公开密码算法,以保证特殊领域的信息安全。这些密码算法的密钥和算法本身都是保密的。为了加强系统的安全性,这些密码算法在使用时会不定期地进行修改。因此,各个通信部门应该能够快速协商和修改密码算法和密钥,以降低泄露的概率,这也是在特殊领域实施密码算法的重要要求。

(3)国内安全应用中,两类密码体制长期共存。国际密码体制主要是指AES-RSA体系密码体系,该密码体系由美国主导,对应的商业产品成熟,技术生态体系完备,但存在一定的系统性安全隐患。中国主导的密码体系是商密体系,主要算法包括SM2/3/4等。随着大力推广,近些年已经形成成熟的技术体系。国家密码局发布SM系列算法的相关标准和规范。2018年,SM2/3/9也成为了ISO/IEC国际标准,标志着国标体系已经初步成型。在国内的安全应用中,两类密码体制均被采用,并在未来很长一段时期,共存运行。这将要求匹配国内安全场景的高速密码处理器支持更多的加密算法。

(4)在具体的实现过程中,密码处理器的设计制造过程存在算法信息泄露和硬件级别的木马植入风险。当前,我国EDA工具和制造工艺不能做到完全自主可控,在非公有算法高性能芯片的设计制造过程中,存在算法本身敏感信息泄露、硬件木马植入等安全隐患。

03

下一代高速密码处理器的探索

当前网络加密流量场景越来也多,叠加带宽的升级,对密码性能的需求逐渐增多。同时国内专用的高速商密处理器比较稀缺,性能与国际主流产品有一定距离。在商用领域,国际上采用多核NP架构的产品性能已经能覆盖5Gbps到100Gbps的范围。但其产品主要支持国际密码体系,对国内商密场景支持欠佳。硬件级别的整合是高速密码芯片的另一个趋势。

整合分为两个方向,一是密码模块向CPU整合,二是单纯的算法芯片向全功能的安全处理器发展。将高速密码模块嵌入CPU,可以实现片内对高速密码服务的调用,以减少数据的搬运和带宽的限制,增加使用的灵活性。该方案对下游厂商来说更加安全和经济,但高速公钥模块的整合,可能对芯片厂商存在不少的技术和成本上的挑战。另一发展方向是,算法芯片通过集成更多模块(比如秘钥管理,可信计算,PUF,SRIOV等模块),成为全功能的安全协处理器,满足当前安全场景多元化的安全需求。

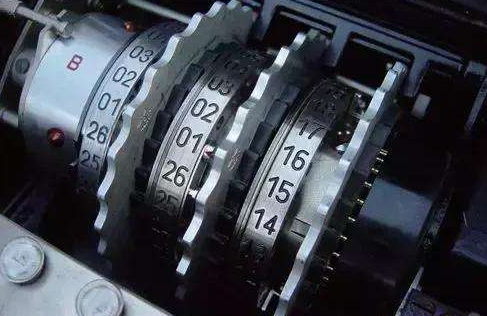

无锡沐创集成电路设计有限公司研发了面向高速场景的下一代密码处理器,旨在探索如何匹配国内应用合规、高灵活和高性能的需求。本次研发的高速安全处理器,将单片的吞吐率提高到了30Gbps,公钥ECC算法达到十万次,同时支持常用国际国内算法。芯片采用粗粒度可重构架构(Coarse-Grained Reconfigurable Architecture,CGRA)。该构架采用配置流和数据流共同驱动的计算模式。如图2所示,计算架构包括控制器和可重构计算阵列,软件经映射工具转化为配置流,并在控制器调度下对计算阵列进行编程。计算阵列的工作分为配置和执行两个阶段:配置阶段由配置流重构计算阵列功能,执行阶段由数据流驱动计算阵列完成任务。

图2芯片中的粗颗粒可重构计算阵列

04

应用场景的探索

4.1数据中心TLS/SSL加速

SSL(Secure Sockets Layer)是一个安全套接层,是一个架构于TCP之上的安全通讯协定。它可以有效协助Internet应用软件提升通讯时的资料完整性以及安全性。后来,标准化之后的SSL名称改为TLS(Transport Layer Security)。

TLS/SSL在实践的过程中,将会带来网络延迟增加、CPU负担过重等一系列问题。TLS/SSL硬件加速器将密码计算任务,通过异步的方式,从CPU卸载到专用的密码协处理器上执行,让CPU分配更多时序到业务相关任务。

图3 SSL的握手流程

4.2国产5G CU服务器

5G无线接入网部分的架构,相对4G来说,进行了一定的演进。4G基站内部分为BBU,RRU和天线几个模块,每个基站都有一套BBU,并通过BBU直接连到核心网。而到了5G时代,原先的RRU和天线合并成了AAU,而BBU则拆分成了DU和CU,每个站都有一套DU,然后多个站点共用同一个CU进行集中式管理(如图4所示)。

在5G的CU服务器中,国内采用的ZUC算法保障传输的安全。通过嵌入高速加密安全处理器,可匹配7~10Gbps的加解密数据流需求。

图4 5G基站架构相对4G架构的变迁

05

结语

当今世界,互联网渗透到人们生活的方方面面,信息安全不仅仅是一个技术问题,更成为了一个社会问题。密码技术作为通信安全和数据安全的基础手段,是网络应用的核心组成部分。高速密码处理器是网络带宽升级,安全应用泛化背景下必然的追求。相较于传统的应用场景,现代安全应用对高速安全处理器要求更高。如何设计高效、灵活的专用密码处理器是信息安全领域的重要研究方向之一。

作者简介>>>

蒋广隶(1989—),男,硕士,产品经理,主要研究方向为高性能密码处理器的应用。

选自《信息安全与通信保密》2020年第11期(为便于排版,已省去原文参考文献)

引用本文:蒋广隶.高速密码处理器的现状与未来[J].信息安全与通信保密,2020(11):34-39.